Name: Id#

## COE 202, Term 142 Digital Logic Design

Quiz#5

Date: Tuesday, May 5, 2015

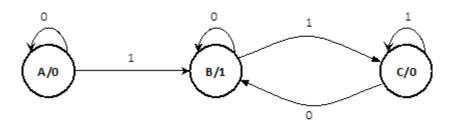

Q1 The figure below shows a state diagram of a sequential circuit with one input x and one output y. Trace the state transitions of this circuit by determining the output and the next state given the sequence of inputs and an initial state as shown in the tables. Assume that the circuit is reset at state A.

(a)

| State | A |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|---|

| X     | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| у     | 0 |   |   |   |   |   |   |   |

(b)

| State | A |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|---|

| X     | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| у     | 0 |   |   |   |   |   |   |   |

- (c) What is the operation that the above circuit performs on the input x? Choose the correct answer:

- i. Multiplication by 2

- ii. Even parity generation

- iii. Odd parity generation

- iv. 2's complement

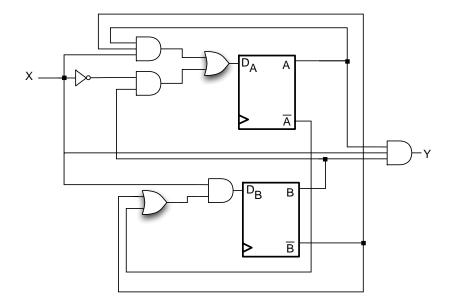

${\bf Q2}$  Consider the sequential circuit below, which has the input X, the output Y and the two D flip-flops A and B.

(a) Is the circuit type Mealy or Moore?

(b) Derive logic expressions for the  $D_A$  and  $D_B$  inputs of the flip-flops and the external output Y.

| (c) | Provide a state table showing {present state and external inputs} and {next state and external output}. |

|-----|---------------------------------------------------------------------------------------------------------|

|     |                                                                                                         |

|     |                                                                                                         |

|     |                                                                                                         |

|     |                                                                                                         |

|     |                                                                                                         |

|     |                                                                                                         |

| (d) | Derive a complete state diagram for the given circuit.                                                  |

|     |                                                                                                         |

|     |                                                                                                         |

|     |                                                                                                         |