Name: KEY Id#

## COE 202, Term 132 Digital Logic Design

## Quiz# 4

Date: Tuesday, April 15

**Q1.** Determine the decimal value of the 7-bit binary number (1011010) when interpreted as:

| An unsigned number | A signed-magnitude number | A signed-1's complement number | A signed-2's complement number |

|--------------------|---------------------------|--------------------------------|--------------------------------|

| 90                 | -26                       | -37                            | -38                            |

ii. Represent the decimal value (- 21) in binary <u>using a total of 7 bits</u> in the following notations:

| A signed-magnitude number | A signed-1's complement number | A signed-2's complement number |  |

|---------------------------|--------------------------------|--------------------------------|--|

| 1010101                   | 1101010                        | 1101011                        |  |

iii. Perform the following signed-2's complement arithmetic operations in binary using 5 bits. All numbers given are represented in the signed-2's complement notation. Indicate clearly the <u>carry values from the last two stages</u>. For each of the three operations, check and indicate whether overflow occurred or not.

| 01010                             | a. 01101 +13<br>+10110 +-10<br>00011 +31 | b. 01010 -11001 00111 -(-7) +17  October 01010 +00111 10001 | c. 11010 co110 -6 -00100 - +4 -10 -10 -11100 -11100 |

|-----------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|

| Overflow<br>Occurred?<br>(Yes/No) | NO                                       | Yes                                                         | NO                                                  |

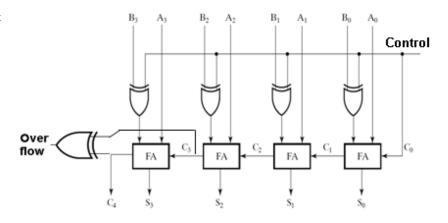

**(B)** Consider the 2's complement 4-bit adder/subtractor hardware shown **(FA** = full adder).

i. Fill in the spaces in the table below.

|    | Inputs |               |         | Outputs        |                |                | Octobele    |             |

|----|--------|---------------|---------|----------------|----------------|----------------|-------------|-------------|

|    | A      | В             | Control | S (binary)     | C <sub>4</sub> | C <sub>3</sub> | Overflow    | 0111        |

|    | 0111   | 0101          | 0       | 1100           | 0              | 1              | 1           | +0101       |

|    | 1010   | 1101          | 1       | 1101           | 0              | 0              | 0           | 1100        |

| 12 |        | -bit adder is |         | s design? (Cir | cle the        | соггес         | et answer): | 1010 - 1010 |

ii. What type of 4-bit adder is used in this

- Carry-ripple adder

- Carry-look-ahead adder

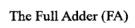

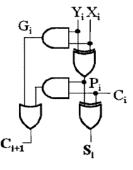

b. Consider a 2-bit version of the hardware above which is shown below. Shown also is full adder used. Given that each basic gate (i.e. AND, OR, NOT) has a delay of  $\tau$  ns and the XOR gate has a delay of  $3\tau$ :

i. Express, as a function of  $\tau$ , the longest time interval needed for the hardware to perform an operation on the two 2-bit numbers.

on the two 2-bit numbers.

$$(3 + 3 + 2 + 3) = 11$$

ii. If such an operation must be performed in no longer than 33 ns, calculate the maximum basic gate delay allowed.