Name: KEY Id#

## COE 202, Term 131 Digital Logic Design

## Quiz# 4

Date: Tuesday, Nov. 25

- **Q1**. Design a circuit that accepts two 2-bit unsigned numbers  $A = A_1A_0$  and  $B = B_1B_0$ . The circuit produces A B when A > B, and produces A + B otherwise. Find the following:

- (a) The number of outputs produced by the circuit.

A - B result is at most 2 bits, A + B result is at most 3 bits  $\Rightarrow$  # outputs = 3

(b) The truth table of the circuit.

| $A_1$ | $A_0$ | $B_1$ | $B_0$ | $O_2$ | $O_1$ | $O_0$ |

|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 0     | 1     | 0     | 0     | 1     |

| 0     | 0     | 1     | 0     | 0     | 1     | 0     |

| 0     | 0     | 1     | 1     | 0     | 1     | 1     |

| 0     | 1     | 0     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 1     | 0     | 1     | 0     |

| 0     | 1     | 1     | 0     | 0     | 1     | 1     |

| 0     | 1     | 1     | 1     | 1     | 0     | 0     |

| 1     | 0     | 0     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     | 0     | 1     |

| 1     | 0     | 1     | 0     | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     | 1     | 0     | 1     |

| 1     | 1     | 0     | 0     | 0     | 1     | 1     |

| 1     | 1     | 0     | 1     | 0     | 1     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     | 1     |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     |

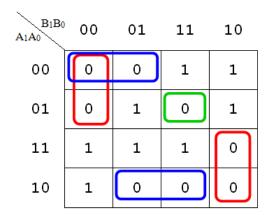

(c) The minimal <u>product-of-sums</u> expression for each output.

| $A_1A_0$ | 00 |  | 01 | 11 |   | 10 |  |

|----------|----|--|----|----|---|----|--|

| 00       | 0  |  | 0  | 0  | 0 |    |  |

| 01       | 0  |  | 0  | 1  |   | 0  |  |

| 11       | 0  |  | 0  | 1  |   | 0  |  |

| 10       | 0  |  | 0  | 1  | 1 |    |  |

$$O_2 = (A_1 + A_0)(\overline{A_0} + B_0)B_1$$

$$O_{1} = (A_{1} + A_{0} + B_{1})(A_{1} + B_{1} + B_{0})(\overline{A_{1}} + A_{0} + \overline{B_{0}})(\overline{A_{1}} + \overline{B_{1}} + B_{0})(A_{1} + \overline{A_{0}} + \overline{B_{1}} + \overline{B_{0}})$$

| B <sub>1</sub> B <sub>0</sub> | 00 |  | 01 | 11 | 10 |   |

|-------------------------------|----|--|----|----|----|---|

| 00                            | 0  |  | 1  | 1  | 0  |   |

| 01                            | 1  |  | 0  | 0  | 1  |   |

| 11                            | 1  |  | 0  | 0  | 1  |   |

| 10                            | 0  |  | 1  | 1  | 0  |   |

|                               |    |  |    |    |    | • |

$$O_0 = (A_0 + B_0)(\overline{A_0} + \overline{B_0})$$

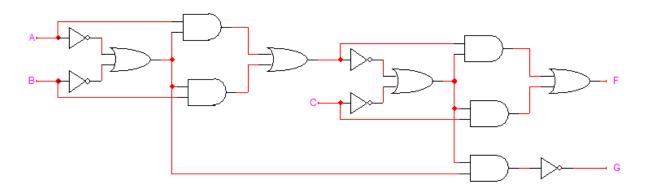

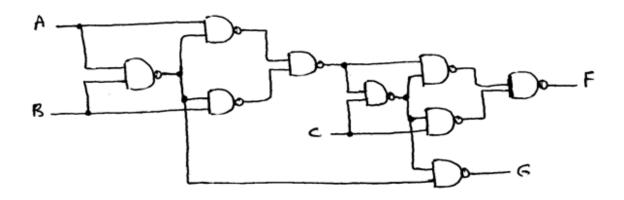

## Q2. Convert the AND/OR/NOT logic diagram shown below to a NAND logic diagram: