## COE 202, Term 151 Digital Logic Design

## Quiz#3

Date: Sunday, Oct. 25

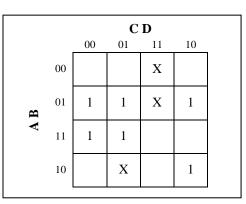

- **Q1**. <u>Assuming the availability of all variables and their complements</u>, simplify the following two Boolean functions F and G subject to the given don't care conditions d1 and d2 using the K-Map method:

- (a) Implement F using only NOR gates:  $F(A, B, C, D) = \sum_{i=1}^{n} A_i \cdot \sum_{i=1}^{n$

$$F(A, B, C, D) = \sum (4, 5, 6, 10, 12, 13)$$

$$d1(A, B, C, D) = \sum (3, 7, 9)$$

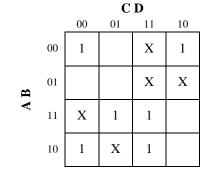

(b) Implement G using only NAND gates:

G(A, B, C, D) =

$$\Sigma$$

(0, 2, 8, 11, 13, 15)

d2(A, B, C, D) =  $\Sigma$ (3, 6, 7, 9, 12)

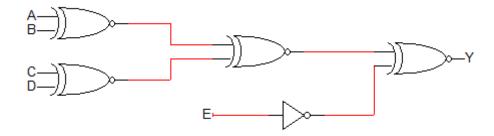

Q2. Implement the following circuit using only 2-input XOR gates with minimal number of gates: