## COE 202, Term 162 Digital Logic Design

## **HW# 4 Solution**

**Q.1.** Obtain the 1's and 2's complement of the following binary numbers: 01100, 00001,00000.

| Number    | 1's complement | 21s Complement |

|-----------|----------------|----------------|

| olloo     | 1 00 11        | 10100          |

| 0 0 00 1  | 11110          | 11111          |

| 0 0 0 0 0 | 1 11 11        | 00000          |

| -         |                |                |

**Q.2.** Find the 10's complement of  $(935)_{11}$ .

10 10 10 10 10

$$\frac{9}{175}$$

**Q.3.** Show how the decimal integer -120 would be represented in 2's complement notation using 8 bits and 16 bits, respectively.

- **Q.4.** Perform subtraction with the following binary numbers using 2's complement and 1's complement, assuming that numbers are represented in 6 bits. Check the answer by straight subtraction:

- (i) 11010 1101

- (ii) 11010 10000

- (iii) 10010 10011

0 10010

- **Q.5.** A microcontroller uses 8-bit registers. Give the following in both binary and decimal:

- (i) The maximum unsigned number that can be stored.

(ii) The smallest (negative) number and the largest (positive) number that can be stored using the sign-magnitude notation.

(11) Sign-magnitude

Smallest negative number

$$-(2-1) = -127$$

largest positive number

$$2^{7}-1 = +127$$

$0 | 11 | 11 | 1$

(iii) The smallest (negative) number and the largest (positive) number that can be stored using the 2's complement notation.

(iii) 21s complement

Smallest regative number

$$-\frac{8-1}{2} = -\frac{7}{2} = -128 \qquad 1000 \ 0000$$

Targest positive number

$$+\frac{7}{2}-1 = 127 \qquad 0111 \ 1111$$

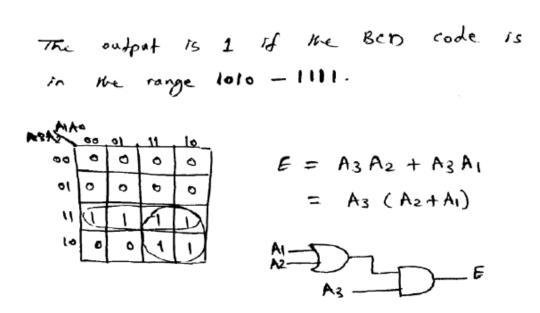

**Q.6.** Design a combinational circuit that detects an error in the representation of a decimal digit in BCD. In other words, obtain a logic diagram whose output is equal to 1 when the inputs contain any one of the six unused bit combinations in the BCD code.

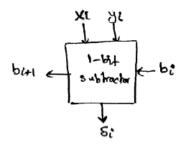

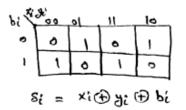

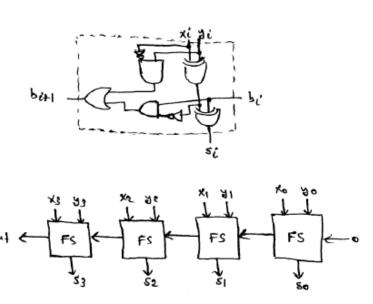

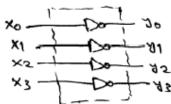

**Q.7.** It is required to design a 4-bit ripple-borrow subtractor to find the subtraction X-Y for the two unsigned numbers,  $X=X_3-X_0$ , and  $Y=Y_3-Y_0$ . Design a 1-bit full subtractor and show how it can be used to construct the 4-bit subtractor.

| bi | Χį | Ji  | 641 | si |

|----|----|-----|-----|----|

| 0  | 0  | 0   | 0   | 0_ |

|    | ٥  | . 1 | 1   |    |

| 00 | 1  | 0   | 0   | 1_ |

| 0  | 1  | 1   | 0   | 0  |

| 1  | ٥  | 0   | 1   |    |

| ī  | 0  | 1   | 11  | 0_ |

| ī  | 1  | 0   | 0   | 6  |

| 1  | 1  | 1   | ı   | 1  |

|    |    |     |     |    |

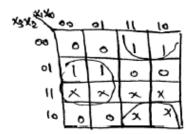

**Q.8.** Design two simplified combinational circuits that generate the 9's complement of (a) a BCD digit and (b) an excess-3 digit. Then compare the gate and literal count of the two circuits. Assume in both cases that input combinations not corresponding to decimal digits give don't care outputs.

## 915 complement

(a) BCD digit

| Digit | x3 x2 X1 X0 | 83 Y2 31 80 |

|-------|-------------|-------------|

| 0     | 0000        | 1 0 0 1     |

| _ \   | 0 0 0 1     | 1 000       |

| 2.    | 0010        | 0 111       |

| 3     | 0011        | 0 110       |

| 4     | 0 1 0 0     | 0 1 0 1     |

| 5     | 0 101       | 0 100       |

| 6     | 0 1 1 0     | 0 0 1 1     |

| 7     | 0 1 1 1     | 0 0 1 0     |

| 8     | 1000        | 0 0 0 1     |

| 9     | 1000        | 0 0 0 0     |

$$\begin{array}{rcl}

32 & = & \times_2 \overline{\times_1} & + & \overline{\times_2} \times_1 \\

& = & \times_2 \bigoplus \times_1

\end{array}$$

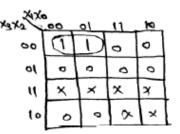

| र्माका व्य | x3 x2 X1 X0 | 33 42 31 30 |

|------------|-------------|-------------|

| 0          | 0011        | 1 1 0 0     |

| 1          | 0 100       | 1011        |

| 2          | 0 1 0 1     | 1010        |

| 3          | 0 1 1 0     | 1001        |

| 4          | 0 111       | 1000        |

| 5          | 1000        | 0 1 1 1     |

| 6          | 1001        | 0 1 1 0     |

| 7          | 1 0 10      | 0 1 0 1     |

| 8          | 1 0 11      | 0 100       |

| 9          | 1 100       | 0 0 1 1     |

|            |             |             |

(c) we can see that for the excess-3 code,

the 91s complement circuit has 4 literals

and 4 inverter Bakes. However, for the BCD

code, the 91s complement circuit has 9 likral

and one inverter, one NOR, and one XOR

gate. This is the advantage of using the

excess-3 code as the 91s complement is

obtained by finding the 11s complement of the

code.

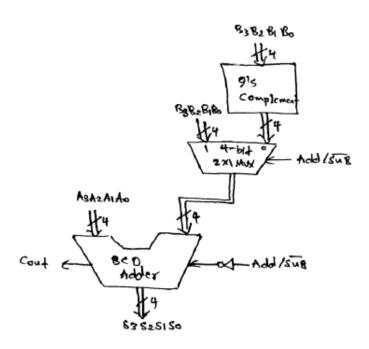

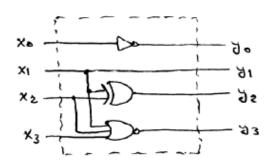

**Q.9.** Construct a BDC adder-subtractor using a BCD adder and the 9's complement designed in Q3, as well as other logic or functional blocks as necessary. Use block diagrams for the components, showing only inputs and outputs where possible.

BCD Adder - Subtractor