### King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

COE 202: Digital Logic Design (3-0-3) Term 151 (Fall 2015-2016) Major Exam 2 Saturday Nov. 21, 2015

Time: 120 minutes, Total Pages: 12

| Name:_ | KEY_ | ID: | Section: |

|--------|------|-----|----------|

|        |      |     |          |

|        |      |     |          |

#### **Notes:**

- Do not open the exam book until instructed

- No Calculators are allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | Maximum Points | Your Points |

|----------|----------------|-------------|

| 1        | 7              |             |

| 2        | 12             |             |

| 3        | 7              |             |

| 4        | 12             |             |

| 5        | 16             |             |

| 6        | 8              |             |

| 7        | 11             |             |

| Total    | 73             |             |

### **Question 1. Choose the correct answer (one answer only)**

**(7 Points)**

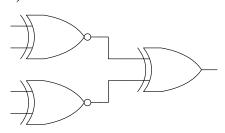

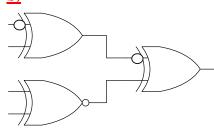

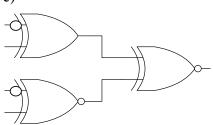

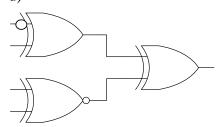

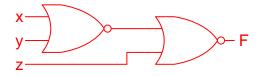

1) Which of the following represents a 4-input XNOR function?

a)

<u>b)</u>

c)

d)

- 2) NOR-OR (NOR first level and OR second level) function implementation is equivalent to:

- a) NAND-OR

- b) AND-NOR

- c) NOR-AND

- d) OR-NAND

- 3) Minimizing the shown k-map results in:

- a) 2 terms, 2-variable each

- b) 2 terms, 1-variable each

- c) 1 term with 2 variables

- d) 1 term with 1 variable

| Х |  | 1 |

|---|--|---|

| 1 |  | 1 |

- 4) Considering F(w, x, y, z), which of the following represents a <u>single</u> prime implicant having the largest area in a k-map (i.e., the largest group of 1's):

- a)  $w + \bar{x} + y + z$

- b)  $wx + \overline{yz}$

- c) <u>yz</u>

- d)  $\overline{w}x\overline{y}z$

Question 2. (12 Points)

1) Represent  $F(x, y, z) = (\bar{x} + z)(x + y + \bar{z})(x + \bar{y} + z)$  in the k-map shown below

|   |   | y z |    |    |    |  |

|---|---|-----|----|----|----|--|

|   |   | 00  | 01 | 11 | 10 |  |

| × | 0 | 1   | 0  | 1  | 0  |  |

|   | 1 | 0   | 1  | 1  | 0  |  |

- 2) Given F(A, B, C, D) shown in the k-map

- a) List all essential prime implicants

$AC, \bar{A}B\bar{C}, A\bar{B}D$

| AB C | D | 00 | 01 | 11 | 10 |

|------|---|----|----|----|----|

| 0    | 0 |    |    |    |    |

| 0    | 1 | 1  | 1  |    |    |

| 1    | 1 | 1  |    | 1  | 1  |

| 1    | 0 |    | 1  | 1  | 1  |

b) Obtain minimized SOP expression of F

$$F = AC + \bar{A}B\bar{C} + A\bar{B}D + \begin{cases} B\bar{C}\bar{D} \\ AB\bar{D} \end{cases}$$

- 3) Given function  $F(w, x, y, z) = \sum (2,4,10,12,14)$  with don't care conditions  $d(w, x, y, z) = \sum (1,5,6,8)$

- a) Use k-maps to provide minimized POS expression for F

$$F = \bar{z}(x + y)$$

| yz<br>wx | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 0  | ×  | 0  | 1  |

| 01       | 1  | x  | 0  | x  |

| 11       | 1  | 0  | 0  | 1  |

| 10       | x  | 0  | 0  | 1  |

|          |    |    |    |    |

b) Implement F using minimum number of 2-input NOR gates

(2 Points)

Question 3. (7 Points)

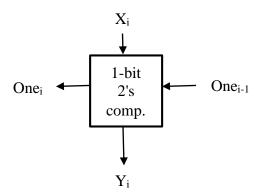

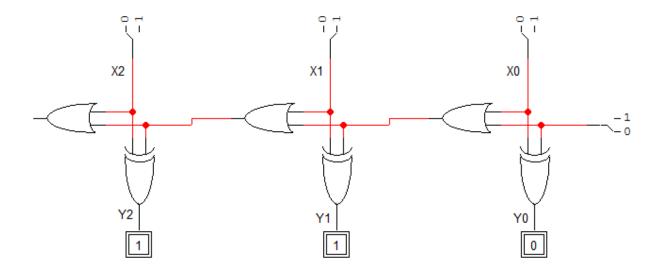

Given an n-bit signed 2's complement number,  $\mathbf{X}$ , it is required to design an iterative combinational circuit to compute the 2's complement of  $\mathbf{X}$ .

- (i) Sow the inputs and outputs of the 1-bit 2's complement iterative cell to be used for designing the n-bit 2's complement circuit. (2 Points)

- (ii) Show the truth table of the 1-bit 2's complement cell.

- (iii) Obtain simplified equations for the outputs of the 1-bit 2's complement cell using only the following gate types: NOT, AND, OR, XOR. (2 Points)

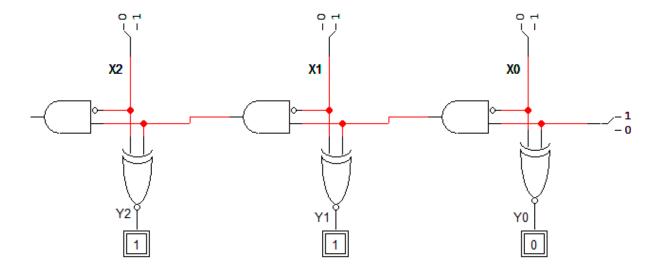

- (iv) Using the 1-bit 2's complement cell, draw a block diagram for a circuit to compute the 2's complement of a 3-bit number X. (1 Point)

We will us a signal (One) that propagates between cells to indicate whether we have got one or not.

| One <sub>i-1</sub> | Xi | Onei | Yi |

|--------------------|----|------|----|

| 0                  | 0  | 0    | 0  |

| 0                  | 1  | 1    | 1  |

| 1                  | 0  | 1    | 1  |

| 1                  | 1  | 1    | 0  |

$$Y_i = X_i \oplus One_{i-1}$$

$One_i = One_{i-1} + X_i$

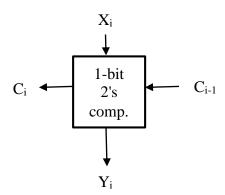

## **Alternative Solution:**

We will us a signal (Cin) that propagates between cells to indicate whether we have carry or not. The 2's complement will be computed as the 1's complement + 1.

| Ci-1 | Xi | Ci | Yi |

|------|----|----|----|

| 0    | 0  | 0  | 1  |

| 0    | 1  | 0  | 0  |

| 1    | 0  | 1  | 0  |

| 1    | 1  | 0  | 1  |

$$Y_i = (X_i \oplus C_{i\text{-}1})' \qquad \qquad C_i = C_{i\text{-}1} \ X_i'$$

Question 4. (12 Points)

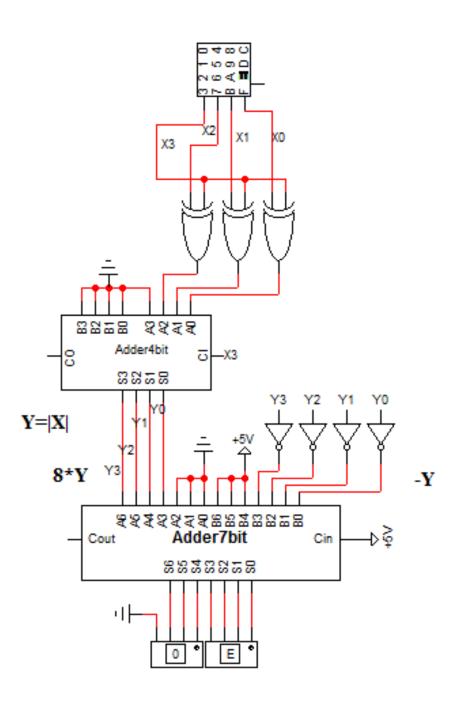

(i) It is required to design a circuit to compute the equation Y=|7\*X|, i.e., Y is equal to the absolute value of 7\*X, where X is a **4-bit signed number in 2's complement representation**. Your circuit should be designed using the minimum number and sizes of the following MSI components (Adders, Multiplexers) and additional logic gates if needed. Show clearly the size of all used components.

(7 Points)

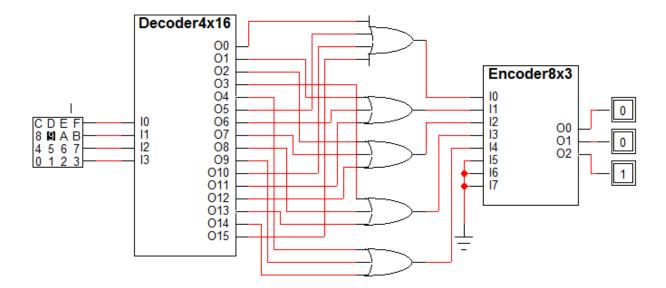

(ii) It is required to design a circuit to compute the equation **Y=X mod 5**, i.e. Y is the remainder of dividing X by 5, where is **X is a 4-bit unsigned number**. For example, 9 mod 5=4 and 10 mod 5=0. Your circuit should be designed using the minimum number and sizes of the following MSI components (Decoder, Encoder) and additional logic gates if needed. Show clearly the size of all used components.

(5 Points)

Question 5. (16 Points)

(i) Fill in all blank cells in the table below. [4 points]

| Dinomi             |                                 | Equivalent decimal | value with the binary inter | preted as:            |  |  |

|--------------------|---------------------------------|--------------------|-----------------------------|-----------------------|--|--|

| Binary<br>(6-bits) | Unsigned Signed-magnitude Signe |                    | Signed-1's complement       | Signed-2's complement |  |  |

| (o-bits)           | integer                         | number             | number                      | number                |  |  |

| 110110             | 54                              | -22                | -9                          | -10                   |  |  |

(ii) Fill in all blank cells in the table below. [6 points]

| (11)    |                                         |                                  |                       |  |  |  |  |

|---------|-----------------------------------------|----------------------------------|-----------------------|--|--|--|--|

|         | -                                       | Binary representation in 6 bits: |                       |  |  |  |  |

| Decimal | Signed-magnitude                        | Signed-1's complement            | Signed-2's complement |  |  |  |  |

|         | representation                          | representation                   | representation        |  |  |  |  |

| + 29    | 011101                                  | 011101                           | 011101                |  |  |  |  |

| - 29    | 111101                                  | 100010                           | 100011                |  |  |  |  |

|         | Binary representation in <b>8 bits:</b> |                                  |                       |  |  |  |  |

|         | Signed-magnitude                        | Signed-1's complement            | Signed-2's complement |  |  |  |  |

|         | representation                          | representation                   | representation        |  |  |  |  |

| - 29    | 10011101                                | 11100010                         | 11100011              |  |  |  |  |

(iii) Show how the following arithmetic operations are performed using 6-bit signed 2's-complement system. Check for overflow and mark clearly any overflow occurrences. [6 points]

| 110100<br>- <u>111110</u>    | 110100<br>+ 000010<br>110110 | (1)                  | 110111<br>+111000<br>101111 |                              | (2)                  |

|------------------------------|------------------------------|----------------------|-----------------------------|------------------------------|----------------------|

| 111110<br>+ 111111<br>111101 |                              | Overflow: Yes/No (3) | 001101<br>- <u>111101</u>   | 001101<br>+ 000011<br>010000 | Overflow: Yes/No (4) |

|                              |                              | Overflow: Yes/No     |                             |                              | Overflow: Yes/No     |

Question 6. (8 Points)

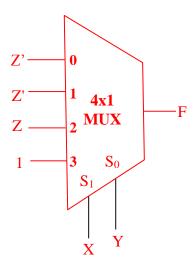

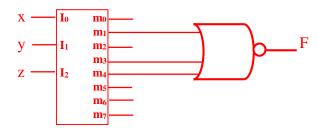

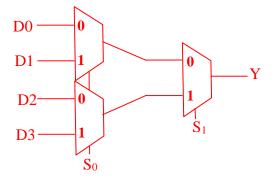

- (i) Show the implementation of the function  $F(x,y,z) = \sum m(0,2,5,6,7)$  [6 points]

- (a) Using a single MUX of minimum size

- (b) Using a minimum size decoder and a single gate with minimum number of inputs

- (a) F has 3 I/Ps  $\rightarrow$  4-to-1 MUX:

| X | Y | Z | F | F  |

|---|---|---|---|----|

| 0 | 0 | 0 | 1 | Z' |

| 0 | 0 | 1 | 0 |    |

| 0 | 1 | 0 | 1 | Z' |

| 0 | 1 | 1 | 0 |    |

| 1 | 0 | 0 | 0 | Z  |

| 1 | 0 | 1 | 1 | L  |

| 1 | 1 | 0 | 1 | 1  |

| 1 | 1 | 1 | 1 | 1  |

(b) Since # of Maxterms is smaller than the # of Minterms, we implement F as POM. Note that  $M_i = m'_i$ , so we need to invert-AND F's Maxterms, i.e. NOR them:

(ii) Implement a 4-to-1 MUX using a minimum number of 2-to-1 MUXs. Clearly mark and label all inputs. [2 points]

Question 7. (11 Points)

(iii) A piece of hardware is described as a Verilog module. One of the given below Verilog codes is the correct description of this piece:

a. Indicate which of these codes is valid and which is invalid fully justifying your answer?

(3 Points)

b. Give the logic diagram of this piece of hardware?

(3 Points)

```

VALID

W

Y

X

| t

| T

| 1 | | k | der

| T = (x+y)| | T = | x | 0 y | 0 t

```

```

\begin{array}{l} \textbf{module} \ V\_Q7A \ (\textbf{output reg} \ z, \ u, \ \textbf{input} \ x, \ w, \ t, \ q); \\ \textbf{wire} \ v, \ y; \\ \textbf{assign} \ y = (q == 1'b1) \ ? \ v : \ w; \ // \text{if} \ q = 1 \ y = v \ \text{else} \ y = w \\ \textbf{always} \ @ (x,y,t) \\ \textbf{begin} \\ z = (x^{y})^{t}; \\ u = (x \& y) \mid (x \& t) \mid (y \& t); \\ \textbf{end} \\ \textbf{not} \ \ (v \ , w); \ // \text{inverter gate instance} \\ \textbf{endmodule} \\ \end{array}

```

#### **INVALID**

(Continuous Assignment cannot be included within an always block)

```

module V_Q7B (output reg z, u, input x, w, t, q); wire v; reg y; always @(x,q,t) begin assign y=(q==1'b1)? v:w; //if q=1 y=v else y=w z=(x^y)^t; u=(x&y) \mid (x&t) \mid (y&t); end not (v,w); //inverter gate instance endmodule

```

#### **INVALID**

(INSTANTATION statement cannot be included within an always block)

```

module V_Q7C (output reg z, u, input x, w, t, q);

reg v, y;

always @(x,q,t, v)

begin

if (q ==1'b1) y = v ; else y = w;

z = (x^y)^t;

u = (x & y) | (x & t) | (y & t);

not (v, w); //inverter gate instance

end

endmodule

```

(iv) You are to write a test bench for the 4-bit adder module which has the following declaration: (5 Points)

## module adder4 (output reg [3:0] sum, output reg cout, input [3:0] A, B);

Use the shown test patterns

| Time Unit | A  | В  |

|-----------|----|----|

| 0         | 5  | 6  |

| 10        | 15 | 9  |

| 20        | 9  | 3  |

| 30        | 13 | 14 |

# Verilog Primitives

- · Basic logic gates only

- and

- ♦ or

- ♦ not

- ♦ buf

- ♦ nand

- ♦ nor

These gates are expandable: 1st node

is O/P node, followed by 1, 2, 3 ...

number of input nodes

# Verilog Operators

| {}      | concater           | nation     |

|---------|--------------------|------------|

| + - * / | / **               | arithmetic |

| %       |                    | modulus    |

| > >= <  | <=                 | relational |

| !       | logical N          | IOT        |

| &&      | logical A          | ND         |

| II      | logical C          | R          |

| ==      | logical equality   |            |

| !=      | logical inequality |            |

| ===     | case equality      |            |

| !==     | case ine           | equality   |

| ?:      | condition          | nal        |

|         |                    |            |

| ~     | bit-wise NOT   |

|-------|----------------|

| &     | bit-wise AND   |

| 1     | bit-wise OR    |

| ^     | bit-wise XOR   |

| ^~ ~^ | bit-wise XNOR  |

| &     | reduction AND  |

| 1     | reduction OR   |

| ~&    | reduction NAND |

| ~     | reduction NOR  |

| ^     | reduction XOR  |

| ~^ ^~ | reduction XNOR |

| <<    | shift left     |

| >>    | shift right    |