## King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

COE 202: Digital Logic Design (3-0-3) Term 112 (Spring 2012) Major Exam II Thursday April 12, 2012

Time: 150 minutes, Total Pages: 13

| Name: | ID: | <b>Section:</b> |

|-------|-----|-----------------|

|       |     | -               |

## **Notes:**

- Do not open the exam book until instructed

- Calculators are not allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

| Question | <b>Maximum Points</b> | <b>Your Points</b> |

|----------|-----------------------|--------------------|

| 1        | 23                    |                    |

| 2        | 22                    |                    |

| 3        | 10                    |                    |

| 4        | 20                    |                    |

| 5        | 15                    |                    |

| 6        | 15                    |                    |

| Total    | 105                   |                    |

Question 1. (23 points)

(a) For the following Boolean function shown in the K-map:

$F(A, B, C, D)=\Sigma m(0, 1, 2, 5, 6, 7, 10, 12, 13, 14, 15)$

| AB CI | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 1  | 1  | 0  | 1  |

| 01    | 0  | 1  | 1  | 1  |

| 11    | 1  | 1  | 1  | 1  |

| 10    | 0  | 0  | 0  | 1  |

- (i) Identify all the *prime implicants* and the *essential prime implicants* of F.

- (ii) Simplify the Boolean function F into a <u>minimal sum-of-products</u> expression.

(b) Consider the following Boolean function  $\mathbf{F}$  together with the don't care conditions  $\mathbf{d}$  shown in the k-map:

$F(A, B, C, D)=\Sigma m(0, 10, 15), d(A, B, C, D)=\Sigma m(1, 2, 4, 8, 11, 14)$

| AB CI | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    | 1  | X  | 0  | X  |

| 01    | X  | 0  | 0  | 0  |

| 11    | 0  | 0  | 1  | X  |

| 10    | X  | 0  | X  | 1  |

- (i) Simplify the Boolean function  $\mathbf{F}$  together with the don't care conditions  $\mathbf{d}$ , into  $\underline{\text{minimal sum-of-products}}$  expression.

- (ii) <u>Starting with the sum-of-products expression</u>, implement the function using only **NAND** gates and **Inverters**.

- (iii) <u>Starting with the sum-of-products expression</u>, implement the function using only **NOR** gates and **Inverters**.

Question 2. (22 Points)

Design a circuit that accepts two 2-bit unsigned numbers  $A = A_1A_0$  and  $B = B_1B_0$ . The circuit produces A - B when A > B, and produces A + B otherwise. Find the following:

- (a) The number of outputs produced by the circuit.

- (b) The truth table of the circuit.

(c) The minimal  $\underline{product\text{-}of\text{-}sums}$  expression for each output.

Question 3. (10 Points)

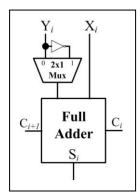

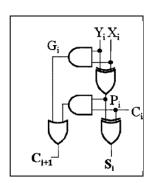

(a) Use the shown circuit on the right to build a 4-bit **adder-subtractor** which can add or subtract two 4-bit numbers X and Y. A mode control input signal **M** is used to define the operation to be performed; if **M=0**, output is (X+Y) while if **M=1**, output is (X-Y).

CLEARLY label ALL inputs and outputs

(b) The Full-Adder circuit is shown to the right. Given the following gate delays;

| Gate/    | Propagation |

|----------|-------------|

| Circuit  | Delay       |

| Inverter | 1 τ         |

| AND, OR  | 2 τ         |

| XOR      | 4 τ         |

| 2x1 Mux  | 5 τ         |

(i) What is the carry propagation delay per Full adder stage?

(ii) For an *n*-bit Ripple-Carry Adder-Subtractor using the circuit of part (a), what is the total delay for the  $n^{th}$  sum bit and the  $(n+1)^{th}$  carry-out bit?

(Clearly identify each delay component)

Question 4. (20 Points)

(a) If <u>6-bit registers</u> are used, show the binary number representation of the decimal numbers (+23), (-23), (+11), and (-11) using the following representation systems:

|                              | +23 | -23 | +11 | -11 |

|------------------------------|-----|-----|-----|-----|

| Signed magnitude system      |     |     |     |     |

| Signed 1's complement system |     |     |     |     |

| Signed 2's complement system |     |     |     |     |

(b) Provide the decimal equivalent of each of the following **signed 2's complement** numbers:

| Signed 2's Complement Number | Equivalent Decimal Number |

|------------------------------|---------------------------|

| 001101                       |                           |

| 010011                       |                           |

| 101101                       |                           |

| 110011                       |                           |

(c) If <u>6-bit registers</u> are used, perform the following <u>signed 2's complement</u> arithmetic operations on the provided signed 2's complement numbers. For each case, state whether the result is correct or an <u>overflow</u> has occurred.

| Signed 2's Complement Arithmetic Operation | Correct Answer or Overflow? |

|--------------------------------------------|-----------------------------|

| (i) 001101 – 101101                        |                             |

|                                            |                             |

|                                            |                             |

|                                            |                             |

| (ii) 010011 – 001101                       |                             |

|                                            |                             |

|                                            |                             |

|                                            |                             |

| (iii) 101101 + 110011                      |                             |

|                                            |                             |

|                                            |                             |

|                                            |                             |

| Question 5.                                                                                        | (15 Points)  |

|----------------------------------------------------------------------------------------------------|--------------|

| Given the function $F(A, B, C) = A B + \overline{A} C$                                             |              |

| (a) Implement F using a single 2-to-1 MUX with no additional gates. Properly label a output lines. | ll input and |

|                                                                                                    |              |

|                                                                                                    |              |

|                                                                                                    |              |

|                                                                                                    |              |

|                                                                                                    |              |

| (b) Implement F using a 4-to-1 MUX. Properly label all input and output lines.                     |              |

|                                                                                                    |              |

| (c) Implement F using a single 3-to-8 decoder, and a single NOR gate. Properly label all input and output lines.                 |

|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

|                                                                                                                                  |

| (d) Implement F using two 2-to-4 decoders with enable, one inverter, and one OR gate. Properly label all input and output lines. |

|                                                                                                                                  |

|                                                                                                                                  |

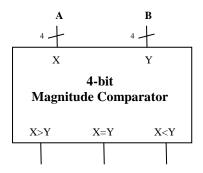

Question 6. (15 points)

- (a) Given two 4-bit signed 1's complement numbers  $\bf A$  and  $\bf B$ ; for  $\bf A=1010$  and  $\bf B=1101$ ;

- (i) What are the corresponding decimal values of A and B?

$$A=1010 = ()_{Decimal}$$

$$B=1101 = ()_{Decimal}$$

(ii) If these values of A and B are applied to the shown magnitude comparator circuit, what are the values of the resulting outputs?

$$(\mathbf{X} > \mathbf{Y}) = \underline{\hspace{1cm}}$$

$$(\mathbf{X} = \mathbf{Y}) = \underline{\hspace{1cm}}$$

$$(\mathbf{X} < \mathbf{Y}) = \underline{\hspace{1cm}}$$

- (b) Given two 4-bit signed 1's complement numbers **A** and **B**, design the following circuits using any number of the following components: XOR gates, decoders, encoders, multiplexers, adders, and/or magnitude comparators:

- (i) A circuit whose 4-bit output **Z** equals the larger of either **A** or **B** given that both **A** and **B** are positive values.

- (ii) A circuit whose 4-bit output **Z** equals the larger of either **A** or **B** given that both **A** and **B** are negative values (*Hint: use conclusions of part* (a)).

- (iii) A circuit whose 4-bit output **Z** equals the larger value of either **A** or **B** given that **A** and **B** may be +ive or -ive in any possible combination.

(You <u>must</u> clearly label the MSI parts used together with all inputs and outputs)