# King Fahd University of Petroleum and Minerals College of Computer Science and Engineering Computer Engineering Department

## COE 202: Digital Logic Design (3-0-3) Term 142 (Spring 2015) Final Exam

**Tuesday May 19, 2015**

7:00 p.m. – 9:30 p.m.

Time: 150 minutes, Total Pages: 12

| Name: | <b>ID:</b> | Section: |

|-------|------------|----------|

|       |            |          |

#### **Notes:**

- Do not open the exam book until instructed

- Calculators are not allowed (basic, advanced, cell phones, etc.)

- Answer all questions

- All steps must be shown

- Any assumptions made must be clearly stated

- Mobile phones must be switched off

| Question | <b>Maximum Points</b> | Your Points |

|----------|-----------------------|-------------|

| 1        | 13                    |             |

| 2        | 18                    |             |

| 3        | 10                    |             |

| 4        | 6                     |             |

| 5        | 8                     |             |

| 6        | 12                    |             |

| Total    | 67                    |             |

Question 1 (13 Points)

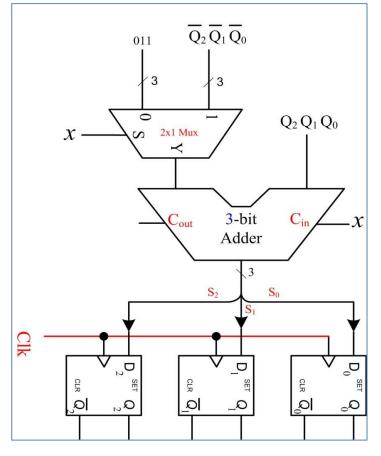

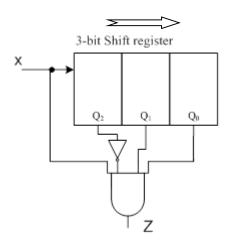

- I. The shown sequential circuit has a single input X and three outputs  $Q_2 Q_1 Q_0$ .

- a. Analyze the circuit and derive its state table. (6 points)

- b. The circuit should have an asynchronous **reset** input, which puts the circuit in initial state **010**. Show how this can be done? **(1 point)**

- c. Is the circuit Moore or Mealy? (1 point)

- d. Briefly describe the function of this circuit. (1 point)

{<u>Note</u>: As shown in the figure, all D-FFs are equipped with asynchronous set (SET) and clear (CLR) inputs}

#### **Solution:**

a.

| PS | 3            |                  | 1          | NS: | ( <b>Q</b> <sub>2</sub> | $\mathbf{Q}_1$ | $\mathbf{Q}_0$ | + |

|----|--------------|------------------|------------|-----|-------------------------|----------------|----------------|---|

| Q  | 2 <b>Q</b> 1 | $\mathbf{Q}_{0}$ | <b>X</b> = | :0  |                         | <b>x</b> =     | 1              |   |

| 0  | 0            | 0                | 0          | 1   | 1                       | 0              | 0              | 0 |

| 0  | 0            | 1                | 1          | 0   | 0                       | 0              | 0              | 0 |

| 0  | 1            | 0                | 1          | 0   | 1                       | 0              | 0              | 0 |

| 0  | 1            | 1                | 1          | 1   | 0                       | 0              | 0              | 0 |

| 1  | 0            | 0                | 1          | 1   | 1                       | 0              | 0              | 0 |

| 1  | 0            | 1                | 0          | 0   | 0                       | 0              | 0              | 0 |

| 1  | 1            | 0                | 0          | 0   | 1                       | 0              | 0              | 0 |

| 1  | 1            | 1                | 0          | 1   | 0                       | 0              | 0              | 0 |

- b. Connect the Reset input to the asynchronous inputs of the 3-FFs {CLR, SET, CLR} respectively.

- c. The outputs  $Q_2$   $Q_1$   $Q_0$  = Present State of the counter independent of  $x \rightarrow$  Moore

- d. The input x acts as synchronous clear input to a mod-8 increment by 3 counter.

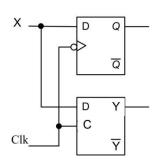

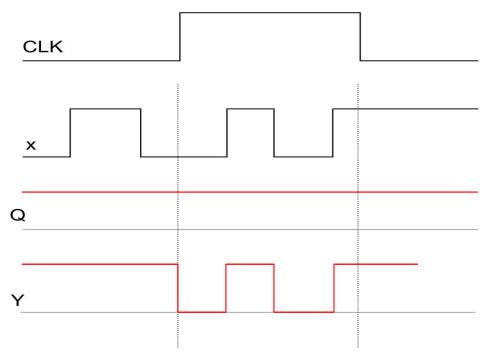

II. For the shown D-latch and D-FF, plot the outputs Q and Y for the shown X – applied signals X and CLK. Assume that the initial state of **both** memory elements to be **1**, and that all delays =0. (**4 points**)

Question 2 (18 Points)

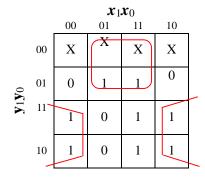

I. The synchronous sequential circuit whose state table is shown has  $\underline{\text{three inputs}}$ ; reset,  $x_1$ , and

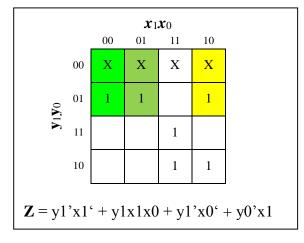

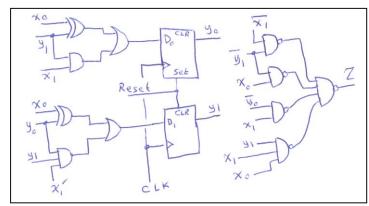

**x**<sub>0</sub> together with a single output **Z**. Assuming state **01** to be the <u>reset state</u>, implement this circuit using D-FFs that have asynchronous set and reset inputs and <u>minimum</u> logic. Draw the detailed logic diagram of your implementation. (**10 points**)

| PS                    | $NS (y_1y_0)^+$ |    |    |    |          | Z  | 7  |    |

|-----------------------|-----------------|----|----|----|----------|----|----|----|

| <b>y</b> 1 <b>y</b> 0 | $x_1x_0$        |    |    |    | $x_1x_0$ |    |    |    |

|                       | 00              | 01 | 11 | 10 | 00       | 01 | 11 | 10 |

| 01                    | 10              | 01 | 01 | 10 | 1        | 1  | 0  | 1  |

| 11                    | 11              | 10 | 01 | 11 | 0        | 0  | 1  | 0  |

| 10                    | 01              | 10 | 11 | 01 | 0        | 0  | 1  | 1  |

II. If, upon powering the circuit on, the initial state was **00** and assuming that the **reset** signal is **not applied**, what would the next state be in case  $x_1x_0=01$  or in case  $x_1x_0=10$ ? (**2 points**)

{*Note:* PS = Present State, and NS = Next State }

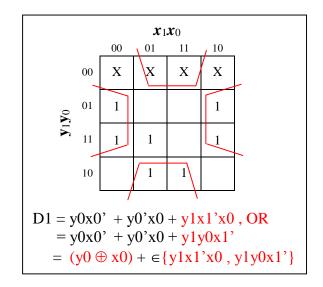

#### **Solution**:

**(I)**

D0 =

$$y1x0' + y1'x0 + y1x1$$

, OR

=  $y1x0' + y1'x0 + x1x0$

=  $(y1 \oplus x0) + \in \{y1x1, x1x0\}$

(II)

| PS | x1x0 | NS  |

|----|------|-----|

| 00 | 0 1  | 1 1 |

| 00 | 1 0  | 0 0 |

III. Write a behavioral Verilog model of a 4-bit register which has the function table given below: (6 points)

| Clr_b | $S_1$ | $S_0$ | Clk        | Function                                                   |

|-------|-------|-------|------------|------------------------------------------------------------|

| 0     | X     | X     | X          | Register Asynchronously cleared                            |

| 1     | 0     | 0     | $\uparrow$ | No Change                                                  |

| 1     | 0     | 1     | $\uparrow$ | Parallel Load ( $Q \leftarrow x$ )                         |

| 1     | 1     | 0     | <b>↑</b>   | Shift left (MSB $\leftarrow$ LSB), (Q[0] $\leftarrow$ Sin) |

| 1     | 1     | 1     | $\uparrow$ | Count Up by 1                                              |

### **Use the following module declaration**:

```

module Q2_Reg (output reg [3:0] Q, input [3:0] x, input Clr_b, Clk, S1, S0, Sin);

```

## **Solution**:

```

\begin{tabular}{ll} \textbf{module} & Q2\_Reg(\textbf{output reg} [3:0] \ Q, \textbf{input} [3:0] \ x \ , \\ & \textbf{input} \ Clr\_b, \ Clk, \ S1, \ S0, \ Sin); \\ \textbf{always} & @(\textbf{posedge} \ Clk, \textbf{negedge} \ Clr\_b) \\ \textbf{if} & (!Clr\_b) \ Q &= 4'h0 \ ; \\ \textbf{else} \\ \textbf{case} & (\{S1,S0\}) \\ & 2'b01: \ Q &= x \ ; \\ & 2'b10: \ Q &= \{Q[2:0],Sin\} \ ; \\ & 2'b11: \ Q &= Q+1 \ ; \\ & \textbf{default}: \ Q &= Q \ ; \\ \textbf{endcase} \\ \textbf{endmodule} \\ \endbedge \en

```

Question 3. (10 Points)

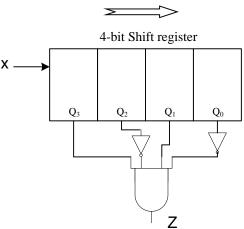

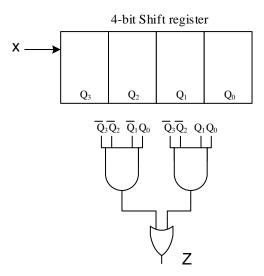

I. A sequence detector has a single input X and a single output Z. The circuit below gives a possible implementation of this detector. Assume that the circuit has a reset input that initializes it to the value  $Q_3Q_2Q_1Q_0=1111$ .

Answer the following questions:

- a. The sequence detected by this circuit is 1010.

- b. The circuit detects {overlapped / non-overlapped} occurrence of the sequence (circle the correct answer)

- c. The circuit output is {Mealy / Moore}. (circle the correct answer)

- II. The circuit below shows an implementation of another sequence detector. Assume that the circuit has a reset input that initializes it to the value  $Q_2Q_1Q_0=000$ .

Answer the following questions:

- a. The sequence detected by this circuit is <u>1011</u>.

- b. The circuit detects {overlapped / non-overlapped} occurrence of the sequence (circle the correct answer)

- c. The circuit output is {Mealy / Moore}. (circle the correct answer)

III. Suggest a Moore circuit that can detect the two sequences 0011 (two 1's followed by two 0's) and 0001 (1 followed by three 0's). What should be the initial state for your circuit to work properly?

Initial state 0000

Question 4. (6 Points)

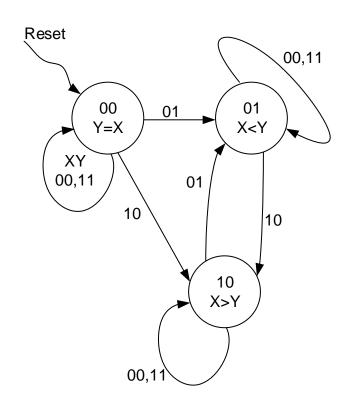

Draw the state diagram of a **MOORE** sequential circuit that receives two serial input numbers (X and Y) starting with the least significant bits (i.e.  $x_0$   $y_0$  then  $x_1y_1$  then  $x_2y_2 ... x_ny_n$ ).

The circuit has two outputs bits  $Z_1Z_0$  as shown in the table.

| Bits of X & Y received thus far | $Z_1Z_0$ |

|---------------------------------|----------|

| X = Y                           | 0 0      |

| X > Y                           | 1 0      |

| X < Y                           | 0 1      |

Assume the availability of an asynchronous reset input to reset the machine to a reset state. A sample input/output data is given below. (**NOTE**: You are *only* required to draw the state diagram, **Nothing MORE**)

| Example: |        | t = 0 | >  | time |    |    |    |

|----------|--------|-------|----|------|----|----|----|

|          | XY     | 10    | 11 | 00   | 01 | 10 | 11 |

|          | output | 00    | 10 | 10   | 10 | 01 | 10 |

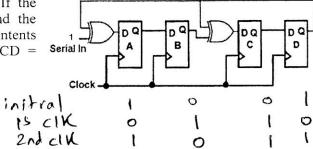

Question 5 (8 Points)

Clock

Consider the shown 4-bit register. If the register contents ABCD = 1001 and the serial input is kept at 1, the register contents after two clock pulses will be ABCD = Serial In Clock

Clock

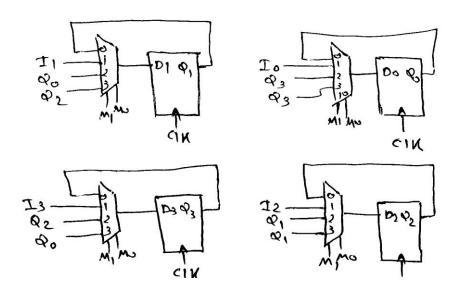

II) Using <u>only</u> D flip-flop(s) and MUX(s) draw the logic diagram for a 4-bit register with 2 mode selection inputs  $M_1M_0$  and 4 load inputs  $I_3I_2I_1I_0$ . The register should operate according to the following table:

| $M_1M_0$ | Register operation                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------|

| 00       | No change.                                                                                                    |

| 01       | <b>Parallel Load</b> : $(Q_3Q_2Q_1Q_0)^+ = I_3I_2I_1I_0$                                                      |

| 10       | <b>Rotate left</b> : $(Q_3Q_2Q_1Q_0)^+ = Q_2Q_1Q_0Q_3$                                                        |

|          | (Examples: 1. register content <u>before</u> rotation = 0110, register content <u>after</u> rotation = 1100   |

|          | 2. register content <u>before</u> rotation = 1110, register content <u>after</u> rotation = 1101)             |

|          | Reverse the order of bits in the register: $(Q_3Q_2Q_1Q_0)^+=Q_0Q_1Q_2Q_3$                                    |

| 11       | (Examples: 1. register content <u>before</u> reversing = 1000, register content <u>after</u> reversing = 0001 |

|          | 2. register content <u>before</u> reversing = 1101, register content <u>after</u> reversing = 1011)           |

You must clearly label the D flip-flop(s) and MUX(s) inputs and outputs. (6 Points)

Question 6 (12 Points)

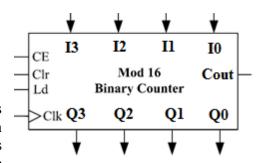

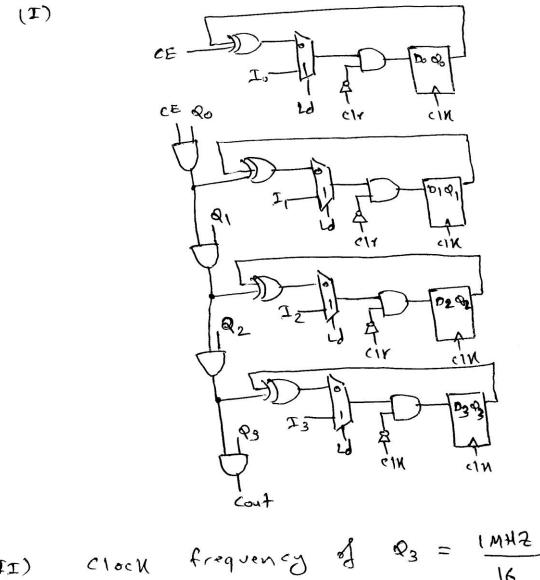

- I) It is required to design a **mod 16** up counter that has the following control inputs:

- **Clr** (synchronous clear),

- **Ld** (parallel load), together with its associated inputs I<sub>3</sub>, I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub>.

- **CE** (Count\_Enable)

Assume that Clr has the highest priority followed by Ld, as illustrated in the table below. The counter produces an output signal ( $C_{out}$ ) which equals 1 when its output equals 15. Design the counter using D-FFs and minimal logic gates. (6 Points)

| Clr | Ld | СЕ | Counter Next Content after the clock pulse $(Q_3Q_2Q_1Q_0)^{\scriptscriptstyle +}$ |

|-----|----|----|------------------------------------------------------------------------------------|

| 1   | X  | X  | 0 0 0 0 (clear)                                                                    |

| 0   | 1  | X  | I3 I2 I1 I0 (load)                                                                 |

| 0   | 0  | 1  | $(Q_3Q_2Q_1Q_0)+1$ (increment up by 1)                                             |

| 0   | 0  | 0  | $Q_3Q_2Q_1Q_0$ (no change)                                                         |

- II) Given that the clock frequency of the mod 16 up counter is 1 MHZ, what is the clock frequency of the Q3 output of the counter? (2 Points)

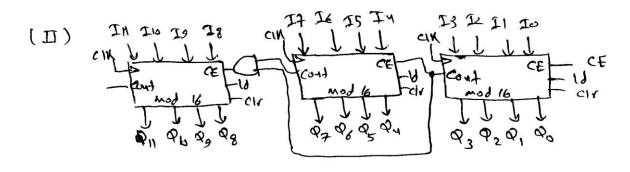

- III) Using any number of the above **mod 16** up counter and other needed logic gates design a **mod 4096**<sup>1</sup> up counter, which has the same control inputs: Clr, LD, and CE. (**4 Points**)

$<sup>^{1}4096 = 2^{12}</sup>$

(II) Clock frequency of

$$Q_3 = \frac{Mh^2}{16}$$

$$= 62.5 \text{ RHZ}$$

# Verilog Operators

| {} co      | ncatenation      |

|------------|------------------|

| + - * / ** | arithmetic       |

| %          | modulus          |

| > >= < <=  | relational       |

| ! log      | gical NOT        |

| && log     | gical AND        |

|            | gical OR         |

| == log     | gical equality   |

| != log     | gical inequality |

| === ca     | se equality      |

| !== ca     | ase inequality   |

| ?: co      | nditional        |

| ~     | bit-wise NOT   |

|-------|----------------|

| &     | bit-wise AND   |

| 1     | bit-wise OR    |

| ۸     | bit-wise XOR   |

| ^~ ~^ | bit-wise XNOR  |

| &     | reduction AND  |

| 1     | reduction OR   |

| ~&    | reduction NAND |

| ~     | reduction NOR  |

| ۸     | reduction XOR  |

| ~^ ^~ | reduction XNOR |

| <<    | shift left     |

| >>    | shift right    |