#### **COE 202, Term 131**

### **Digital Logic Design**

### **Assignment# 3 Solution**

Due date: Thursday Dec. 19

**Q.1.** It is required to design a synchronous sequential circuit that receives BCD digits serially through input  $\mathbf{B_{in}}$  and converts them to excess-3 digits and produces the result serially through output  $\mathbf{B_{out}}$ . Assume the existence of an asynchronous reset input to reset the machine to a reset state. The following is an example of some input and output streams:

#### Example:

| Input  | B <sub>in</sub>  | 000010101011110  |

|--------|------------------|------------------|

| Output | B <sub>out</sub> | 1100000100110101 |

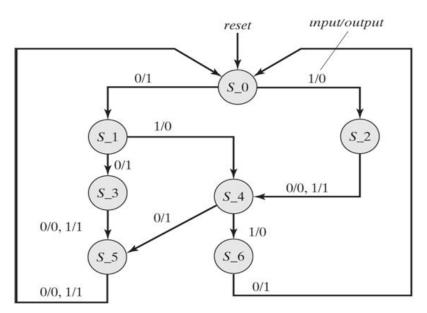

(i) Derive the <u>state diagram</u> of the circuit assuming a <u>Mealy</u> model.

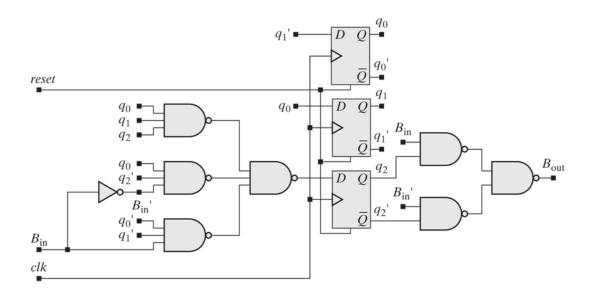

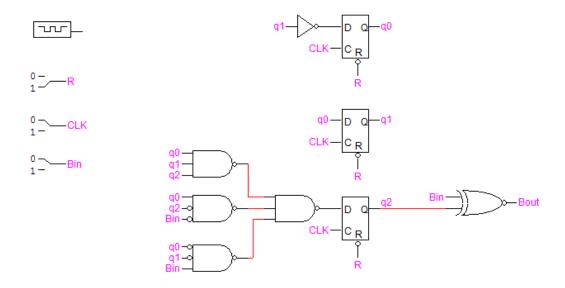

(ii) Implement your design using D flip flops with minimal number of flip flops and combinational logic.

# **State Table:**

| Next state/output table |                   |       |  |  |  |  |  |

|-------------------------|-------------------|-------|--|--|--|--|--|

|                         | Next state/output |       |  |  |  |  |  |

| State                   | Input             |       |  |  |  |  |  |

|                         | 0                 | 1     |  |  |  |  |  |

| S_0                     | S_1/1             | S_2/0 |  |  |  |  |  |

| S_1                     | S_3/1             | S_4/0 |  |  |  |  |  |

| S_2                     | S_4/0             | S_4/1 |  |  |  |  |  |

| S_3                     | S_5/0             | S_5/1 |  |  |  |  |  |

| S_4                     | S_5/1             | S_6/0 |  |  |  |  |  |

| S_5                     | S_0/0             | S_0/1 |  |  |  |  |  |

| S_6                     | S_0/1             | -/-   |  |  |  |  |  |

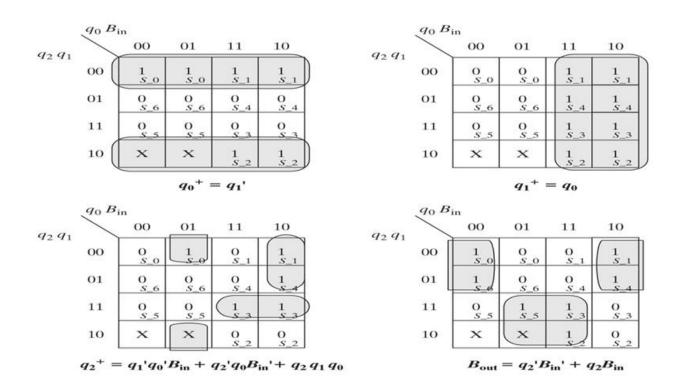

# **State Encoding & State Transition Table:**

| State assigment |       |  |  |  |

|-----------------|-------|--|--|--|

| $q_2 q_1 q_0$   | State |  |  |  |

| 000             | S_0   |  |  |  |

| 001             | S_1   |  |  |  |

| 010             | S_6   |  |  |  |

| 011             | S_4   |  |  |  |

| 100             |       |  |  |  |

| 101             | S_2   |  |  |  |

| 110             | S_5   |  |  |  |

| 111             | S_3   |  |  |  |

| Encoded next state/output table |               |                         |     |        |   |  |  |

|---------------------------------|---------------|-------------------------|-----|--------|---|--|--|

|                                 | State         | Next state              |     | Output |   |  |  |

|                                 | $q_2 q_1 q_0$ | ${q_2}^+{q_1}^+{q_0}^+$ |     |        |   |  |  |

|                                 |               | Input                   |     | Input  |   |  |  |

|                                 |               | 0                       | 1   | 0      | 1 |  |  |

| S_0                             | 000           | 001                     | 101 | 1      | 0 |  |  |

| S_1                             | 001           | 111                     | 011 | 1      | 0 |  |  |

| S_2                             | 101           | 011                     | 011 | 0      | 1 |  |  |

| S_3                             | 111           | 110                     | 110 | 0      | 1 |  |  |

| S_4                             | 011           | 110                     | 010 | 1      | 0 |  |  |

| S_5                             | 110           | 000                     | 000 | 0      | 1 |  |  |

| S_6                             | 010           | 000                     | _   | 1      | _ |  |  |

|                                 | 100           | _                       | _   | _      | _ |  |  |

(iii) Model your design in logic works.

**(iv)** Test your design and verify its correctness by simulation. Show snapshots of your simulation to demonstrate its correctness.

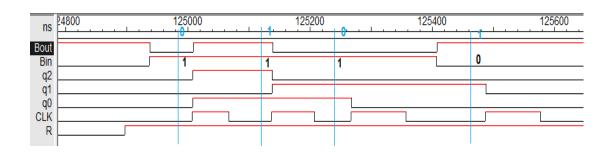

When we will apply the input 0000 (i.e. decimal 0) we get the output 1100 (i.e., decimal 3) as shown in the simulation below:

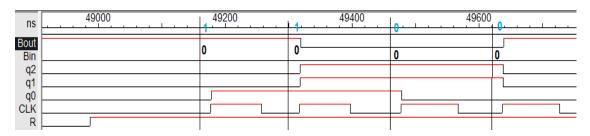

When we will apply the input 1110 (i.e. decimal 7) we get the output 0101 (i.e., decimal 10) as shown in the simulation below: