## **COE 202, Term 131**

## **Digital Logic Design**

## **Assignment# 1 Solution**

Due date: Tuesday, Nov. 12

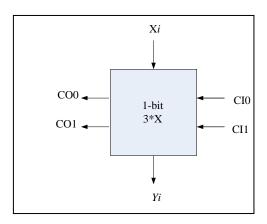

- **Q.1.** It is required to design a combinational circuit that computes the equation Y=3\*X, where X is an n-bit unsigned number.

- (i) Design the circuit as a modular circuit where each module receives a single bit of the input,  $X_i$ .

(ii) Derive the truth table of your 1-bit module in (i).

Truth Table;

| χį  | $CI_1$ | (Io | C01      | (00 | 30 |

|-----|--------|-----|----------|-----|----|

| 0   | 0      | 0   | 0        | 0   | 0  |

| (5) | 0      | 1   | 0        | ۵   | 1  |

| 9   | 1      | O   | 0        | l   | 0  |

| 0   | (      |     | <b>x</b> | X   | X  |

|     | ٥      | 0   | 0        | 1   | 1  |

| 1   | 0      | l   | ).       | Ö   | Ö  |

| (   | 1      | O   | t        | 0   | 1  |

| t   |        | 1   | χ        | χ   | х  |

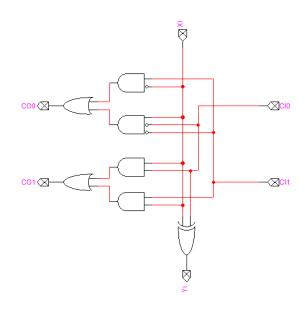

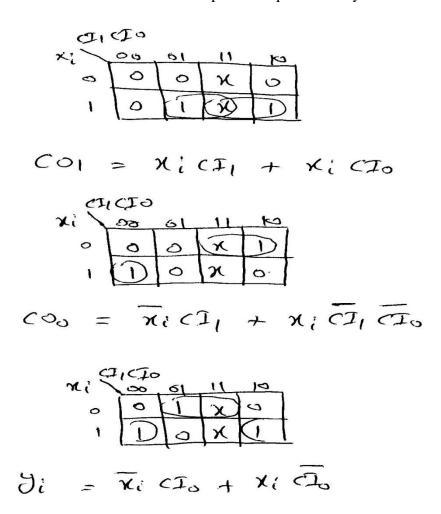

(iii) Derive minimized two-level sum-of-product equations for your 1-bit module circuit.

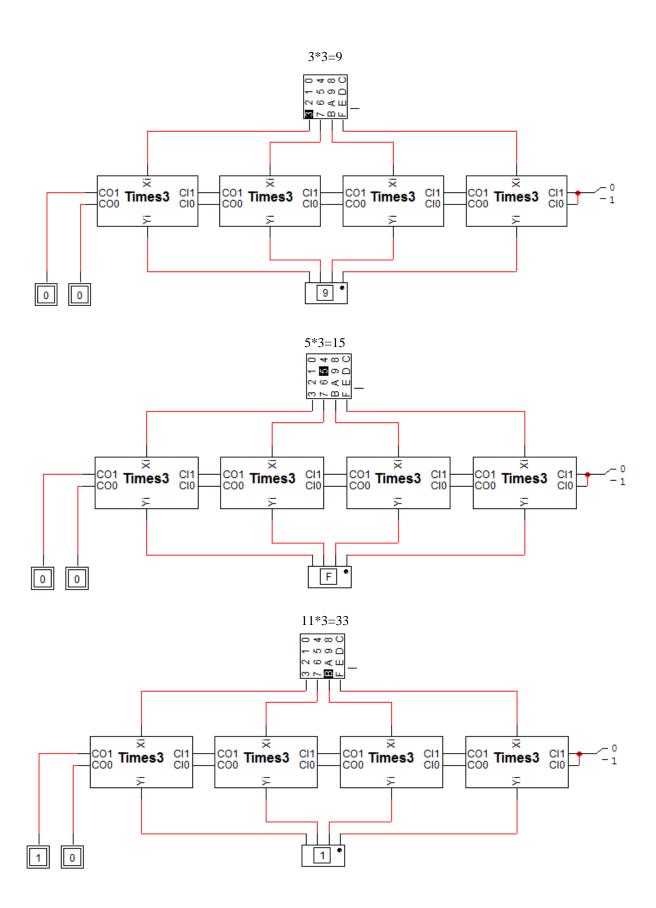

(iv) Verify the correctness of your design by modeling and simulating a 4-bit circuit using LogicWorks.