## **COE 205, Term 032**

## Computer Organization & Assembly Programming Quiz# 7

Date: Sunday, May 18, 2004

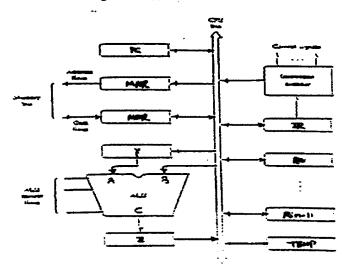

**Q1.** Consider the one-bus CPU organization shown below. Assume that the CPU has only three general registers, namely R0, R1, and R2. Furthermore, assume that the ALU can perform any of the following four functions based on the control signals f1, f2, f3, and f4, as shown below:

*f1*: C=A+B; *f2*: C=A-B; *f3*: C=A+1; *f4*: C=A-1;

- (i) Write the minimum number of control steps required to **fetch** an instruction using this CPU. Assume that the memory is asynchronous and that each instruction occupies one memory location.

- (ii) Write the minimum number of control steps required to **execute** each of the following instructions:

- (a) JE label ; if the zero flag is 1, then jump to label. Assume that Label is a short address.

- (b) SUB J, 5; subtract the constant 5 from the content of memory variable J.

- (c) XCHG R1, R2; exchange the content of register R1 and register R2;

- (d) LOOP label; decrement the content of R0 and then branch conditionally to *label* if the zero flag equals to 0. The branch address is specified using relative addressing mode.

- (iii) Assuming that the instruction set of the CPU consists of only the four instructions mentioned above, determine the logic needed in the encoder of a hardwired control unit for the signal  $PC_{in}$ .

**Q2.** It is required to design a data path to execute the following two types of instructions: *MOV Rdst, Rsrc* and *ADD Rdst, Rsrc*, where *Rsrc* and *Rdst* can be either R0, R1, R2, or R3. Show the data-path design and indicate all the signals needed to control it. Note that you only need to show the interconnection of the registers with the adder i.e., there is no need to show the PC, IR, MAR and MDR registers.