## Problem 1

## Part (A) [10 points]

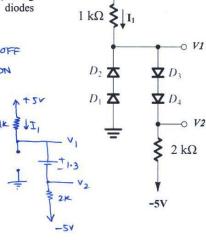

For the circuit shown below find the values of the labeled currents and voltages  $(I_1,\ V_1,\ V_2)$  using the constant voltage model for all diodes  $(V_{DO}{=}0.65V)$ .

$$I_1 = \frac{5 - 1.3 - (-5)}{3k} = 2.9 \, \text{mA}$$

$$V_1 = 5 - 2.9 \, \text{m(lk)} = 2.1 \, \text{V}$$

$$V_2 = 2k(2.9m) - 5 = 0.8V$$

+ 5V

## Part (B) [10 points]

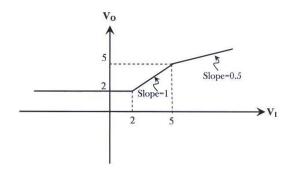

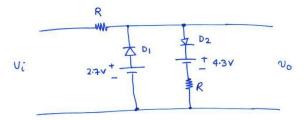

Design a limiter circuit using only two diodes, two batteries and a few resistors to provide the transfer function shown below. Assume that the diodes have a 0.7V drop when they conduct

Specify the value of each component.

One possible solution is as shown.

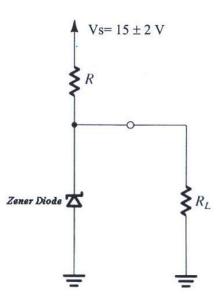

The Zener diode in the circuit shown below is specified to have  $V_Z=8V$  at  $I_Z=4$  mA,  $r_Z=25\Omega$ , and  $I_{Zmin}=0.5$  mA. The supply voltage  $V_S$  is nominally 15 V but can vary by  $\pm 2$  V. The load resistor  $R_L$  is in the range of 4 k $\Omega$  to 6 k $\Omega$ .

- a) Find V<sub>ZO</sub> for this Zener diode.

- b) Find the maximum allowed R that will maintain the circuit to operate as a regulator.

- Find the change in V<sub>O</sub> resulting from the ±2V change in V<sub>S</sub>.

- d) Evaluate this regulator. (Hint: a good regulator has a load regulation less than 30 mV/mA and a line regulation less than 20 mV/V).

a) From the test data and using

$$V_2 = V_{20} + r_2 I_2$$

$$\Rightarrow V_{20} = V_2 - r_2 I_2$$

$$= 8 - 25(4m)$$

$$= 7.9 V$$

c)

$$\Delta V_0 = \Delta V_S \frac{r_2}{r_2 + R}$$

$\approx 2K$

$$= \pm 24.7 \text{ mV}$$

d) LIR =

$$r_2/(R_+r_2) = 12.3 \text{ mV/V}$$

(below standard: Soud)

LOR =  $r_2/(R_+r_2) = 24.7 \text{ mV/mA}$  (below standard: Soud)

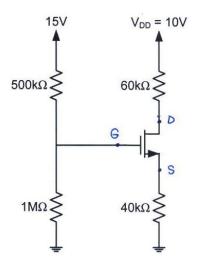

The NMOS transistor in the given circuit has  $V_t = 1$  V, and  $K_n = 25 \mu A/V^2 (K_n = \mu_n C_{ox} W/L)$ .

- a) Find the gate voltage V<sub>G</sub>.

- b) Find the following: drain and source voltages  $V_D$  and  $V_S$ ; drain and source currents  $I_D$  and  $I_S$ . Neglect the channel-length modulation effect (i.e. assume  $\lambda$ =0).

- Explain the phenomenon channel-length modulation; illustrate your answer with a sketch of the cross-section of the NMOS.

b)

$$V_S = 40 \text{ K ID}$$

$V_D = 10 - 60 \text{ K ID} \implies V_{DS} = 10 - 100 \text{ K IDS}$

Assume Saturation

$$I_D = K (VGS - Vt)^2$$

$I_D = \frac{25M}{2} (10 - 40 K I_D - 1)^2$

Solving the quadratic equation

$I_D = 0.14 mA \implies V_D = 1.53 V$

Check assumption:

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

$I_D = 0.14 mA \implies V_D = 1.53 V$

Assume Triode

$$I_D = K \left[ 2(UGS - UE) VDS - VDS \right]$$

$$= \frac{25M}{2} \left( 10 - 100 K I_D \right) \left[ 2(9 - 40 K I_D) - (0 - 100 K I_D) \right]$$

$$\Rightarrow 25K I_D^2 + 8.5 I_D - 1m = 0$$

$$Solve \quad for \quad I_D$$

$$I_D = -0.432 \quad mA \quad (rejected)$$

$$I_D = 0.092 \quad mA$$

$$I_S = 0.092 \quad mA$$

$$V_S = 3.7V$$

$$V_D = 4.48 V$$

$$V_DS = 0.78 V$$

$$Check \quad assumption$$

$$V_D < VG - VE$$

$$0.78 < 10 - 1 \qquad OK$$