## King Fahd University of Petroleum and Minerals Department of Electrical Engineering EE 200 **Dr. Hassan Ragheb** Design project

## This project is due on June 3-2007 4:00 PM. A maximum of 2 students can work together and submit one report.

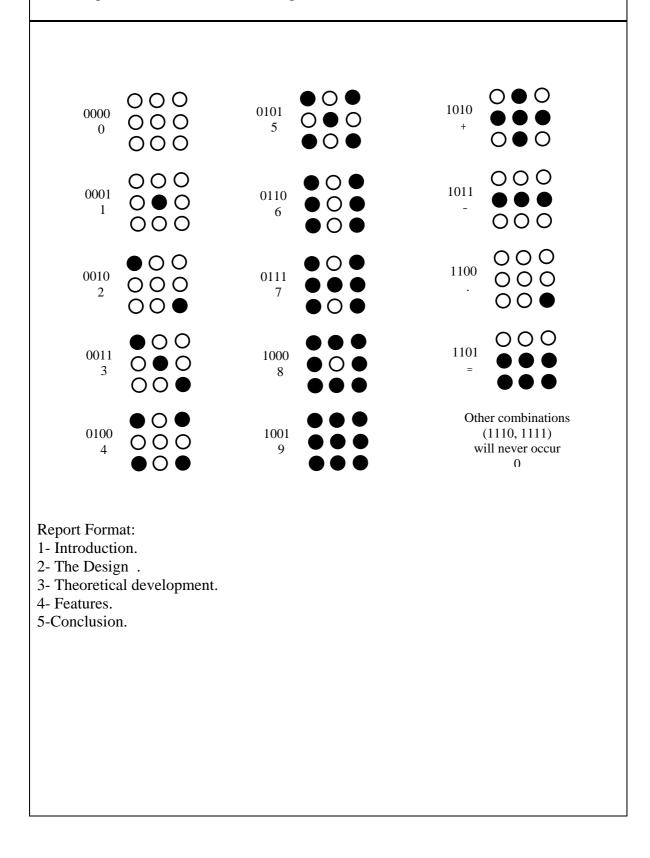

Design a controller to display an electronic 9-dotted die as shown next. A set of these could be used to display decimal numbers and some mathematical equations.

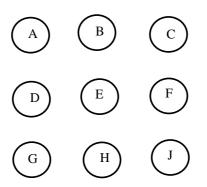

The inputs to the controller represent a 4-bit number *W*, *X*, *Y*, *Z* which indicates what is to be displayed. They are all available both un-complemented and complemented. There are nine outputs, A, B, C, D, E, F, G, H, J, one for each of the dots.

The display comes in two types. The first type requires a 1 to light the display. The second type requires 0 to light the display. For the second version, the outputs of the controller are the complement of the outputs required for the first type of display.

The diagram below shows each of the inputs and the display that results in. A black dot indicates that the bit is lit; a circle indicates not lit. Note that 0 lights none of the lights; 9 lights all of them

- a. Show the truth table for the controller.

- b. Write a minimum sum of products expression for each of the outputs, treating each output as a separate problem. Show both maps and algebraic expressions. For each expression, all terms must be prime implicants of that function. Sharing is possible only if a product term is a prime implicant of more than one function.

- c. Assume that the function found in part b are to be implemented with a two-level NAND gate circuit. Do not build two gates with the same inputs. How many two-input and how many three-input gates are used? (No gates may be used as NOT gates; there is no need for any gates with more than three inputs.) If 7400 (1 package = 4 X ( 2 input) NAND gates) and 7410 (1 package = 3 X ( 3 input) NAND gates) integrated circuit packages were used, how many of each are used?

- d. Show the equations and a block diagram of a minimum cost two-level NAND gate implementation. (of course, there will be sharing, and some of the terms will not be prime implicants of one or more of the functions for which they are used). No gates may be used as NOT gates. How many integrated circuit packages are needed?

- e. We went to implement this, but ran into a problem. All we could find was one 7410 package of three-input NAND gates (three gates in the package). There were

plenty of 7400 packages of two-input gates. Show the equations and a block diagram for an implementation this way. No gates may be used as NOT gates. (It is possible to start with either the solution to part b or d above, or some other set of equations) Use as few 7400s as possible.