# Pipelined Processor Design

COE 301 / ICS 233 Computer Organization Dr. Muhamed Mudawar

College of Computer Sciences and Engineering King Fahd University of Petroleum and Minerals

### Presentation Outline

#### Pipelined Datapath and Control

- Pipeline Hazards

- Data Hazards and Forwarding

- Load Delay, Hazard Detection, and Stall

- Control Hazards

- Delayed Branch and Dynamic Branch Prediction

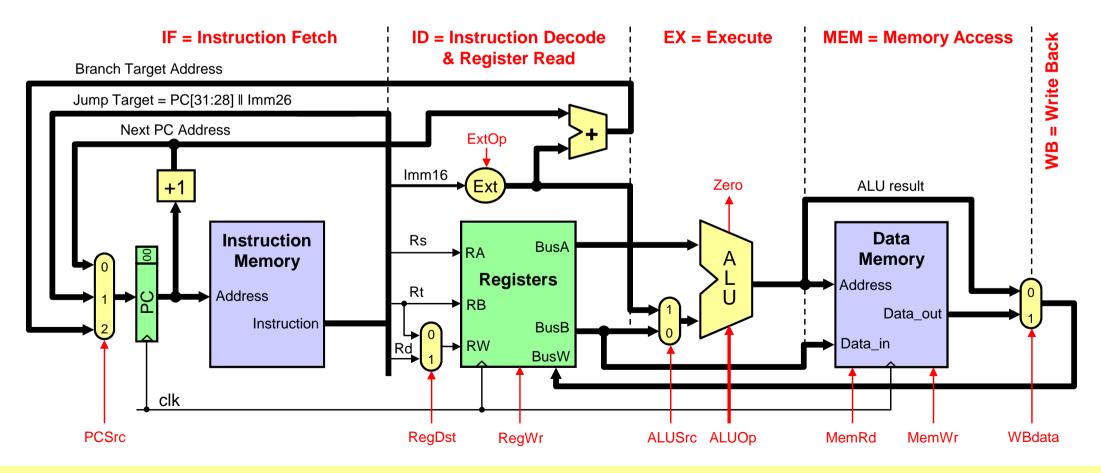

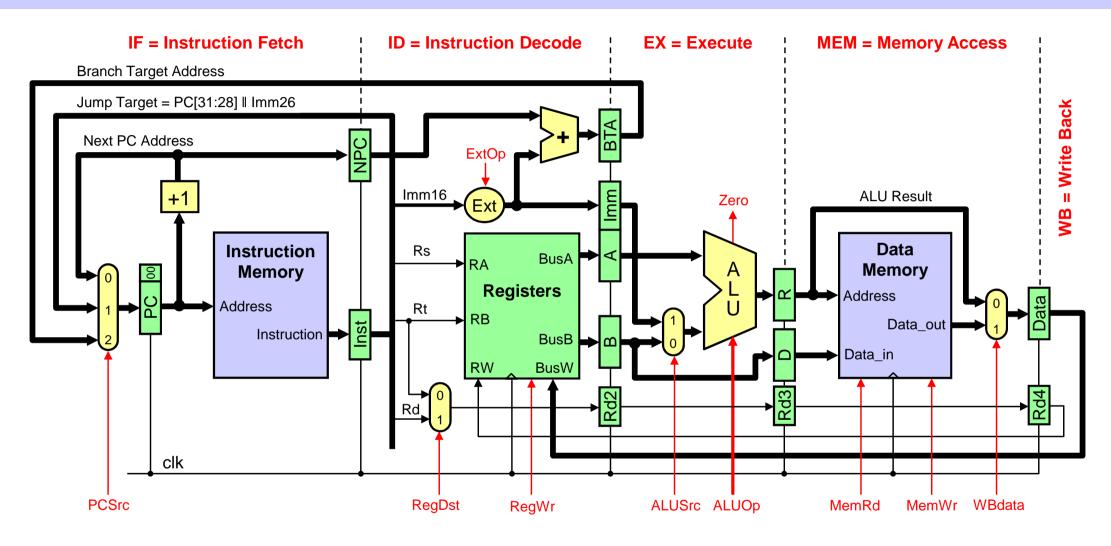

# Single-Cycle Datapath

- Shown below is the single-cycle datapath

- How to pipeline this single-cycle datapath?

- Answer: Introduce pipeline registers at end of each stage

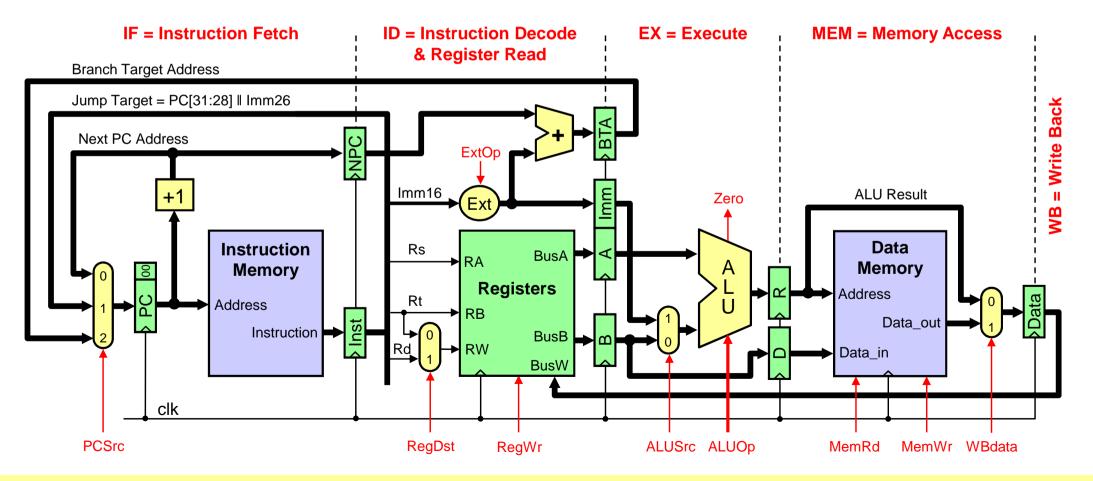

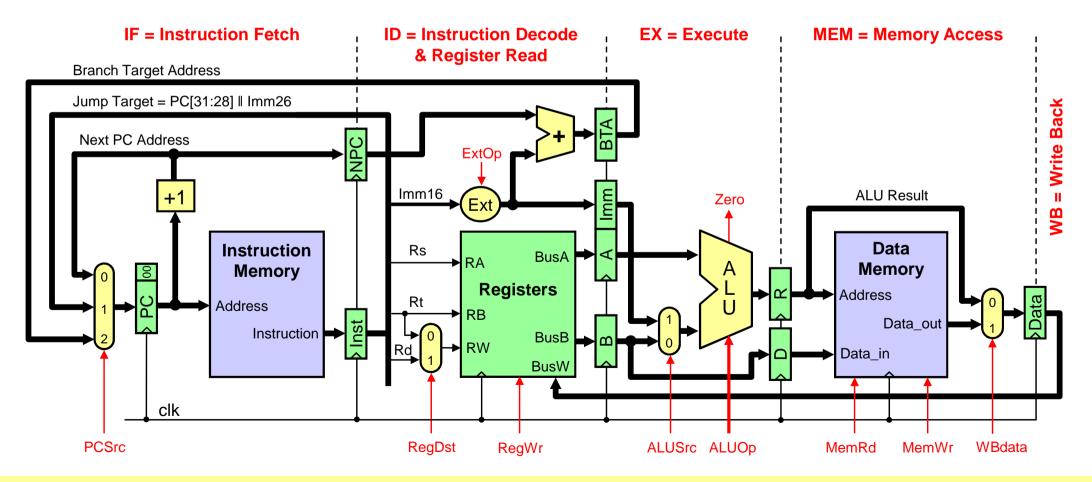

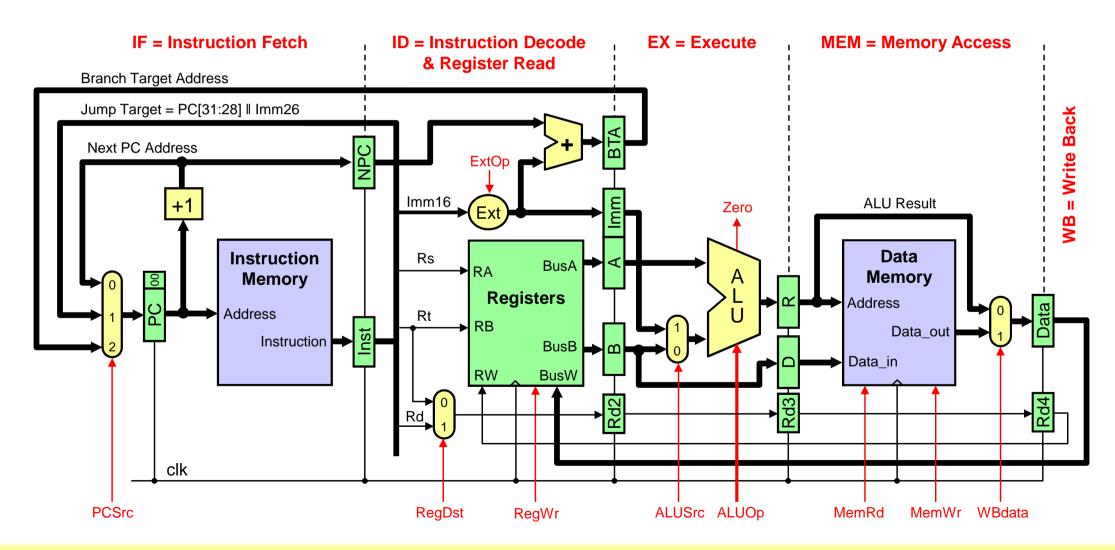

# Pipelined Datapath

- Pipeline registers are shown in green, including the PC

- Same clock edge updates all pipeline registers and PC

- ♦ In addition to updating register file and data memory (for store)

### Problem with Register Destination

- Instruction in ID stage is different from the one in WB stage

- ♦ WB stage is writing to a different destination register

- ♦ Writing the destination register of the instruction in the ID Stage

# Pipelining the Destination Register

- Destination Register should be pipelined from ID to WB

- $\diamond$  The WB stage writes back data knowing the destination register

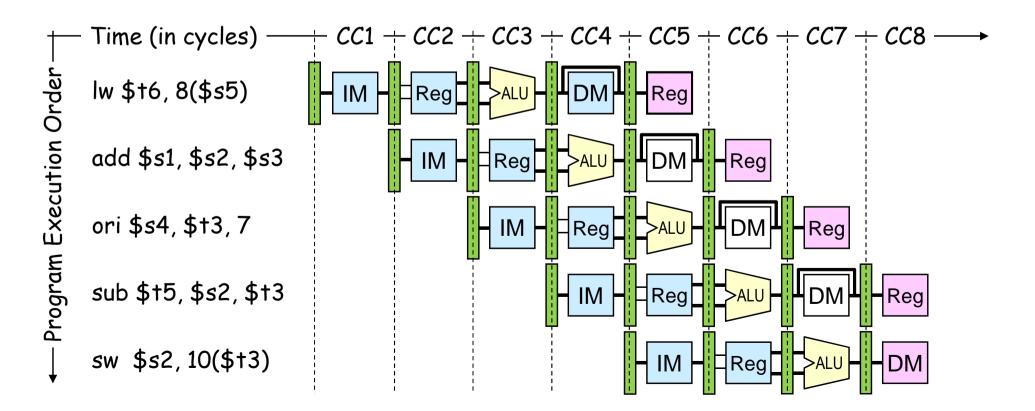

# Graphically Representing Pipelines

- Multiple instruction execution over multiple clock cycles

- ♦ Instructions are listed in execution order from top to bottom

- ♦ Clock cycles move from left to right

- $\diamond$  Figure shows the use of resources at each stage and each cycle

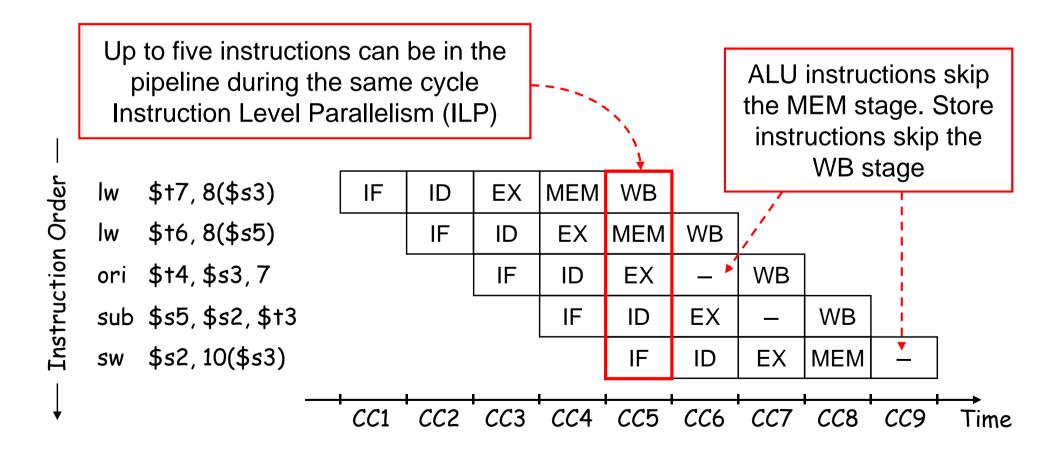

### Instruction-Time Diagram

Instruction-Time Diagram shows:

$\diamond$  Which instruction occupying what stage at each clock cycle

Instruction flow is pipelined over the 5 stages

# **Control Signals**

#### Same control signals used in the single-cycle datapath

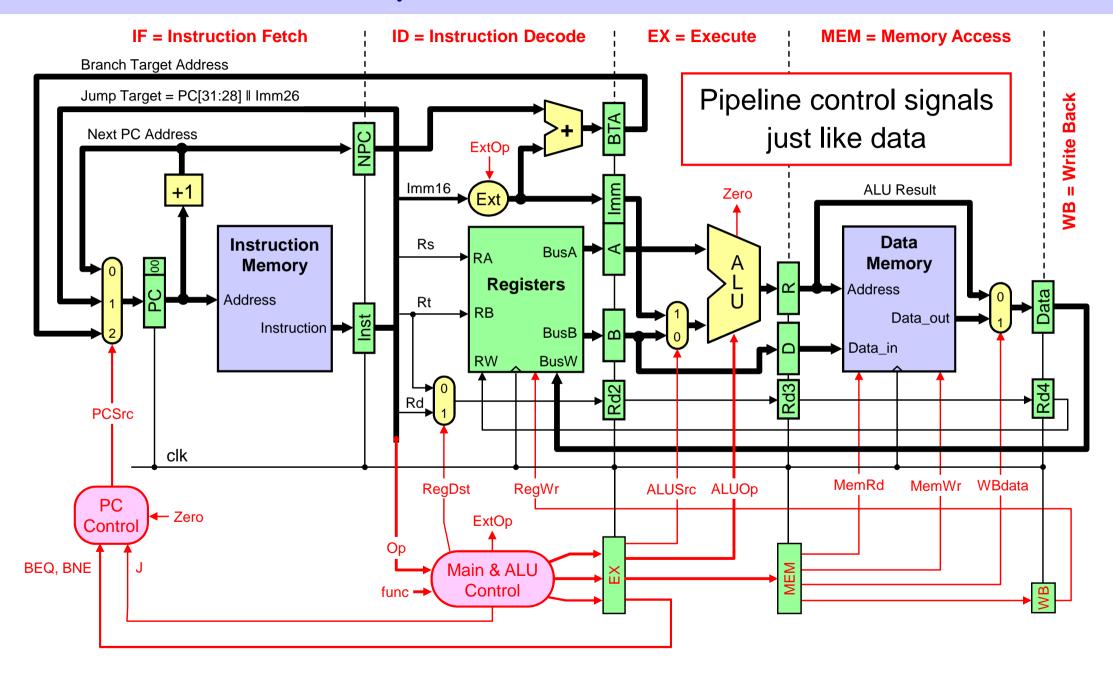

### **Pipelined Control**

### Pipelined Control - Cont'd

- ID stage generates all the control signals

- Pipeline the control signals as the instruction moves

- ♦ Extend the pipeline registers to include the control signals

- Each stage uses some of the control signals

- ♦ Instruction Decode and Register Read

- Control signals are generated

- RegDst and ExtOp are used in this stage, J (Jump) is used by PC control

- ♦ Execution Stage => ALUSrc, ALUOp, BEQ, BNE

- ALU generates zero signal for PC control logic (Branch Control)

- ♦ Memory Stage => MemRd, MemWr, and WBdata

- ♦ Write Back Stage => RegWr control signal is used in the last stage

# Control Signals Summary

| Ор     | Decode<br>Stage |        | Execute<br>Stage |       | Memory<br>Stage |       |        | Write<br>Back | PC<br>Control   |

|--------|-----------------|--------|------------------|-------|-----------------|-------|--------|---------------|-----------------|

|        | RegDst          | ExtOp  | ALUSrc           | ALUOp | MemRd           | MemWr | WBdata | RegWr         | PCSrc           |

| R-Type | 1=Rd            | Х      | 0=Reg            | func  | 0               | 0     | 0      | 1             | 0 = next PC     |

| ADDI   | 0=Rt            | 1=sign | 1=lmm            | ADD   | 0               | 0     | 0      | 1             | 0 = next PC     |

| SLTI   | 0=Rt            | 1=sign | 1=lmm            | SLT   | 0               | 0     | 0      | 1             | 0 = next PC     |

| ANDI   | 0=Rt            | 0=zero | 1=lmm            | AND   | 0               | 0     | 0      | 1             | 0 = next PC     |

| ORI    | 0=Rt            | 0=zero | 1=lmm            | OR    | 0               | 0     | 0      | 1             | 0 = next PC     |

| LW     | 0=Rt            | 1=sign | 1=lmm            | ADD   | 1               | 0     | 1      | 1             | 0 = next PC     |

| SW     | Х               | 1=sign | 1=lmm            | ADD   | 0               | 1     | Х      | 0             | 0 = next PC     |

| BEQ    | Х               | Х      | 0=Reg            | SUB   | 0               | 0     | Х      | 0             | 0 or 2 = BTA    |

| BNE    | Х               | Х      | 0=Reg            | SUB   | 0               | 0     | Х      | 0             | 0 or 2 = BTA    |

| J      | Х               | Х      | Х                | Х     | 0               | 0     | Х      | 0             | 1 = jump target |

PCSrc = 0 or 2 (BTA) for BEQ and BNE, depending on the zero flag

Next...

Pipelined Datapath and Control

Pipeline Hazards

Data Hazards and Forwarding

Load Delay, Hazard Detection, and Stall

Control Hazards

Delayed Branch and Dynamic Branch Prediction

### Pipeline Hazards

#### Hazards: situations that would cause incorrect execution

♦ If next instruction were launched during its designated clock cycle

#### 1. Structural hazards

$\diamond$  Caused by resource contention

♦ Using same resource by two instructions during the same cycle

#### 2. Data hazards

$\diamond$  An instruction may compute a result needed by next instruction

$\diamond$  Data hazards are caused by data dependencies between instructions

#### 3. Control hazards

Caused by instructions that change control flow (branches/jumps)

$\diamond$  Delays in changing the flow of control

Hazards complicate pipeline control and limit performance

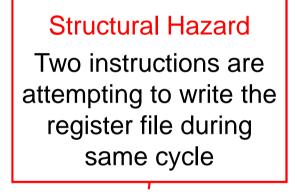

### Structural Hazards

#### Problem

$\diamond\,$  Attempt to use the same hardware resource by two different

instructions during the same clock cycle

#### Example

- ♦ Writing back ALU result in stage 4

- $\diamond$  Conflict with writing load data in stage 5

### Resolving Structural Hazards

#### Serious Hazard:

$\diamond$  Hazard cannot be ignored

#### Solution 1: Delay Access to Resource

- ♦ Must have mechanism to delay instruction access to resource

- $\diamond$  Delay all write backs to the register file to stage 5

- ALU instructions bypass stage 4 (memory) without doing anything

#### Solution 2: Add more hardware resources (more costly)

- ♦ Add more hardware to eliminate the structural hazard

- ♦ Redesign the register file to have two write ports

- First write port can be used to write back ALU results in stage 4

- Second write port can be used to write back load data in stage 5

### Data Hazards

- Dependency between instructions causes a data hazard

- The dependent instructions are close to each other

- $\diamond\,$  Pipelined execution might change the order of operand access

- Read After Write RAW Hazard

- $\diamond$  Given two instructions *I* and *J*, where *I* comes before *J*

- $\diamond$  Instruction J should read an operand after it is written by I

- ♦ Called a data dependence in compiler terminology

- I: add **\$s1**, **\$s2**, **\$s3** # **\$s1** is written

- J: sub \$s4, \$s1, \$s3 # \$s1 is read

- $\diamond$  Hazard occurs when *J* reads the operand before *I* writes it

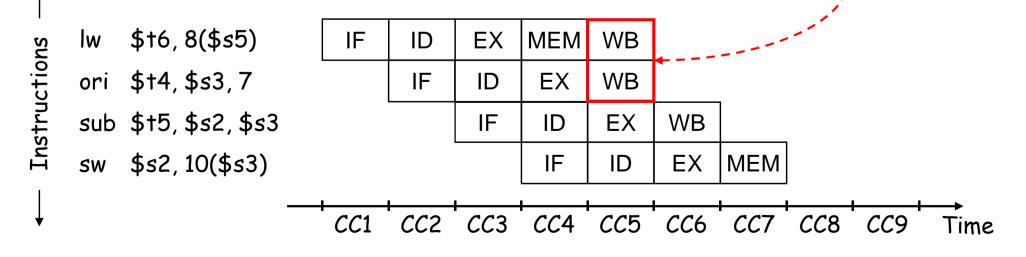

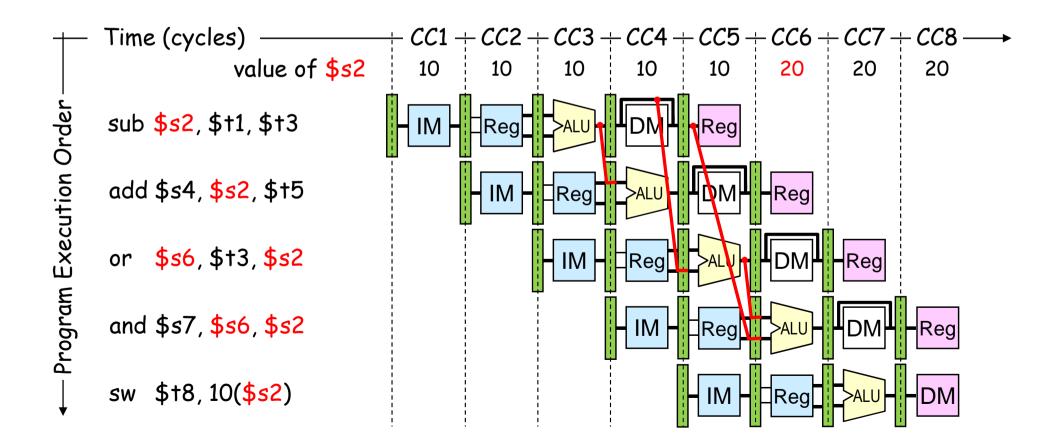

# Example of a RAW Data Hazard

Result of sub is needed by add, or, and, & sw instructions

Instructions add & or will read old value of \$s2 from reg file

During CC5, \$s2 is written at end of cycle, old value is read

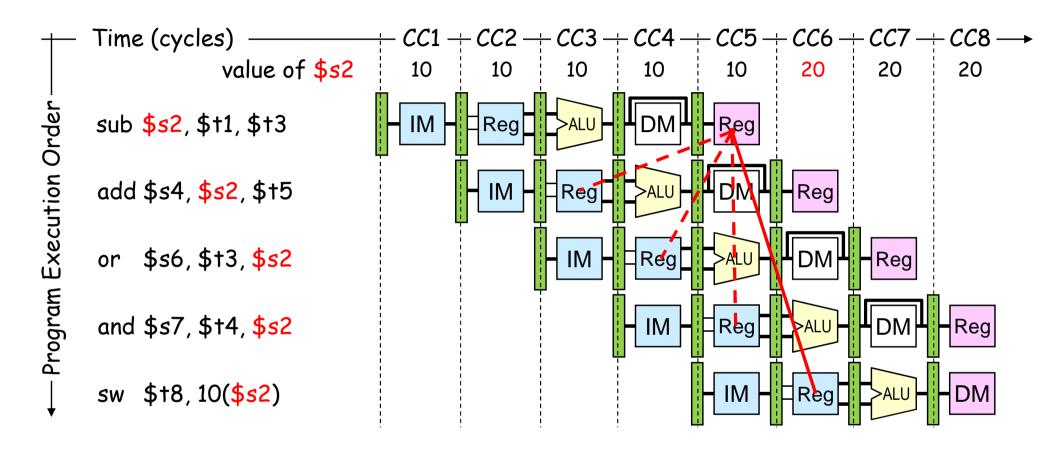

# Solution 1: Stalling the Pipeline

- Three stall cycles during CC3 thru CC5 (wasting 3 cycles)

- The 3 stall cycles delay the execution of add and the fetching of or

- $\diamond$  The 3 stall cycles insert 3 bubbles (No operations) into the ALU

- The add instruction remains in the second stage until CC6

- The or instruction is not fetched until CC6

### Solution 2: Forwarding ALU Result

The ALU result is forwarded (fed back) to the ALU input

$\diamond$  No bubbles are inserted into the pipeline and no cycles are wasted

✤ ALU result is forwarded from ALU, MEM, and WB stages

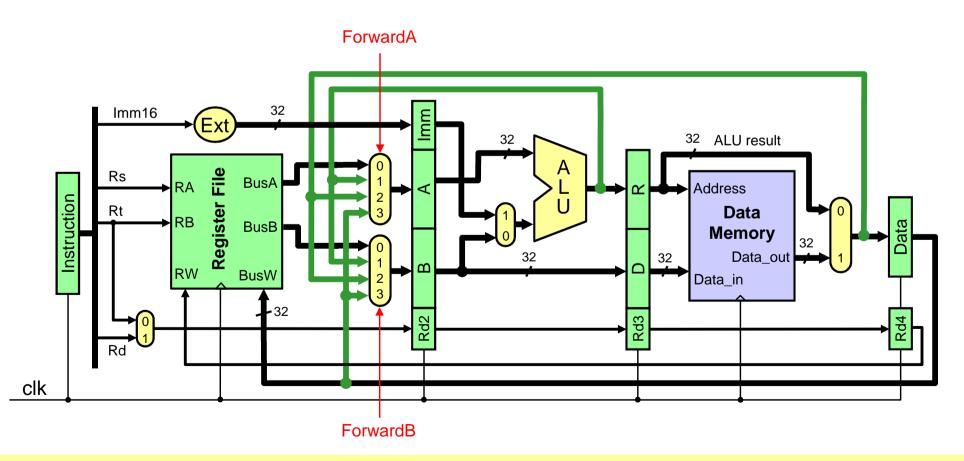

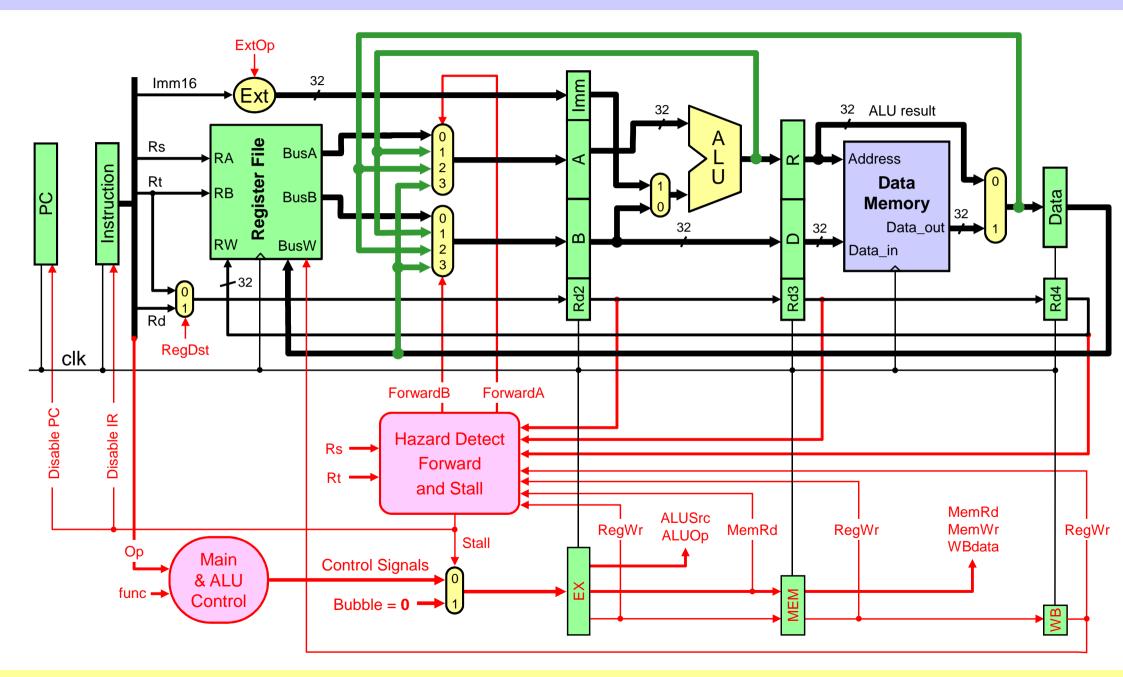

### **Implementing Forwarding**

- Two multiplexers added at the inputs of A & B registers

- ♦ Data from ALU stage, MEM stage, and WB stage is fed back

- Two signals: ForwardA and ForwardB to control forwarding

# Forwarding Control Signals

| Signal       | Explanation                                                                  |  |  |  |

|--------------|------------------------------------------------------------------------------|--|--|--|

| ForwardA = 0 | First ALU operand comes from register file = Value of (Rs)                   |  |  |  |

| ForwardA = 1 | Forward result of previous instruction to A (from ALU stage)                 |  |  |  |

| ForwardA = 2 | Forward result of 2 <sup>nd</sup> previous instruction to A (from MEM stage) |  |  |  |

| ForwardA = 3 | Forward result of 3 <sup>rd</sup> previous instruction to A (from WB stage)  |  |  |  |

| ForwardB = 0 | Second ALU operand comes from register file = Value of (Rt)                  |  |  |  |

| ForwardB = 1 | Forward result of previous instruction to B (from ALU stage)                 |  |  |  |

| ForwardB = 2 | Forward result of 2 <sup>nd</sup> previous instruction to B (from MEM stage) |  |  |  |

| ForwardB = 3 | Forward result of 3 <sup>rd</sup> previous instruction to B (from WB stage)  |  |  |  |

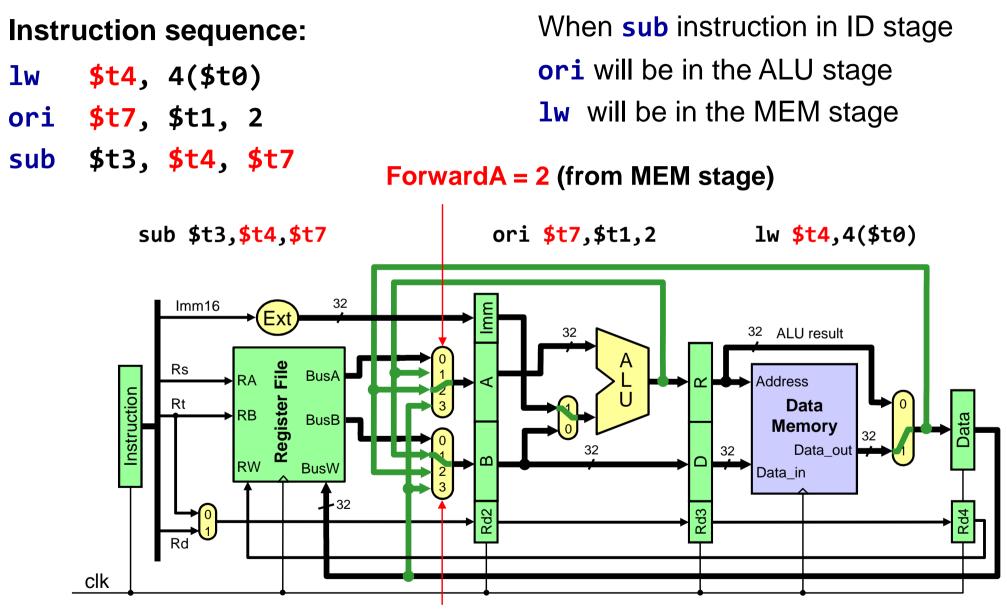

# Forwarding Example

#### ForwardB = 1 (from ALU stage)

### **RAW Hazard Detection**

- Current instruction is being decoded in the Decode stage

- Previous instruction is in the Execute stage

- Second previous instruction is in the Memory stage

- Third previous instruction is in the Write Back stage

If ((Rs != 0) and (Rs == Rd2) and (EX.RegWr)) ForwardA = 1

Else if ((Rs != 0) and (Rs == Rd3) and (MEM.RegWr)) ForwardA = 2

Else if ((Rs != 0) and (Rs == Rd4) and (WB.RegWr)) ForwardA = 3

Else ForwardA = 0

If ((Rt != 0) and (Rt == Rd2) and (EX.RegWr)) ForwardB = 1

Else if ((Rt != 0) and (Rt == Rd3) and (MEM.RegWr)) ForwardB = 2

Else if ((Rt != 0) and (Rt == Rd4) and (WB.RegWr)) ForwardB = 3

Else ForwardB = 0

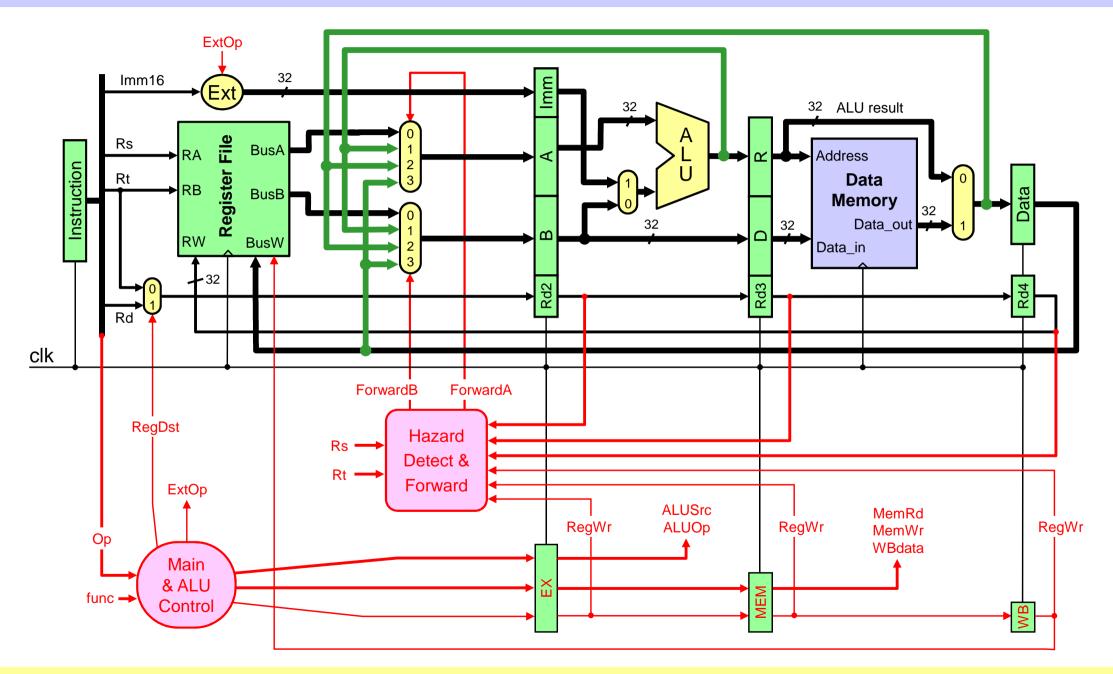

# Hazard Detecting and Forwarding Logic

COE 301 / ICS 233 – Computer Organization

Next...

Pipelined Datapath and Control

Pipeline Hazards

Data Hazards and Forwarding

Load Delay, Hazard Detection, and Stall

Control Hazards

Delayed Branch and Dynamic Branch Prediction

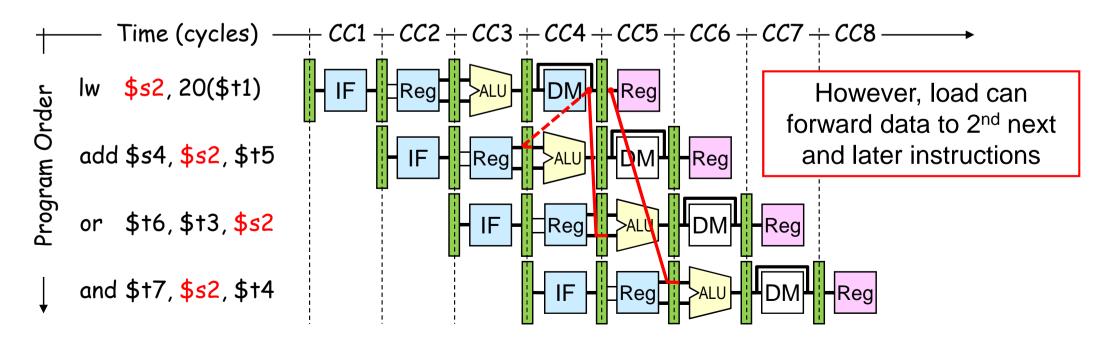

# Load Delay

Unfortunately, not all data hazards can be forwarded

Load has a delay that cannot be eliminated by forwarding

✤ In the example shown below …

♦ The LW instruction does not read data until end of CC4

Cannot forward data to ADD at end of CC3 - NOT possible

### Detecting RAW Hazard after Load

- Detecting a RAW hazard after a Load instruction:

- ♦ The load instruction will be in the EX stage

- $\diamond$  Instruction that depends on the load data is in the decode stage

- Condition for stalling the pipeline

if((EX.MemRd == 1) // Detect Load in EX stage

and (ForwardA==1 or ForwardB==1)) Stall // RAW Hazard

- Insert a bubble into the EX stage after a load instruction

- ♦ Bubble is a no-op that wastes one clock cycle

- ♦ Delays the dependent instruction after load by one cycle

- Because of RAW hazard

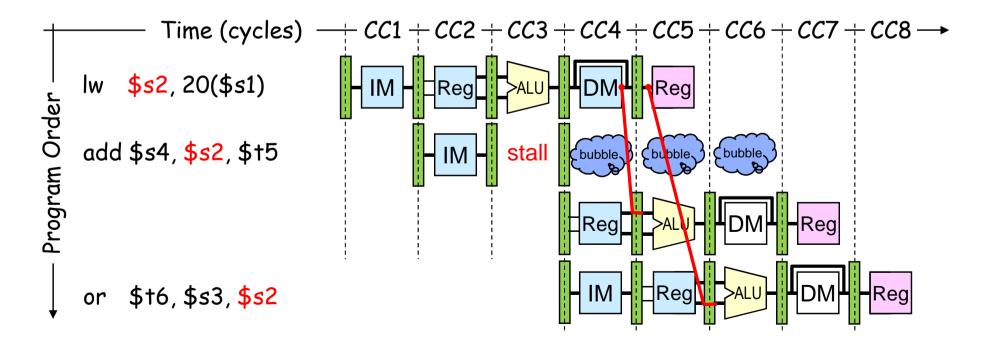

### Stall the Pipeline for one Cycle

♦ ADD instruction depends on LW → stall at CC3

- Allow Load instruction in ALU stage to proceed

- Freeze PC and Instruction registers (NO instruction is fetched)

- ♦ Introduce a bubble into the ALU stage (bubble is a NO-OP)

Load can forward data to next instruction after delaying it

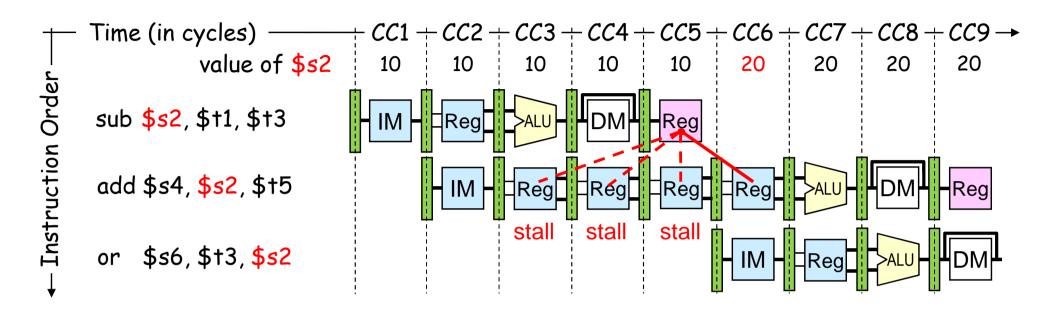

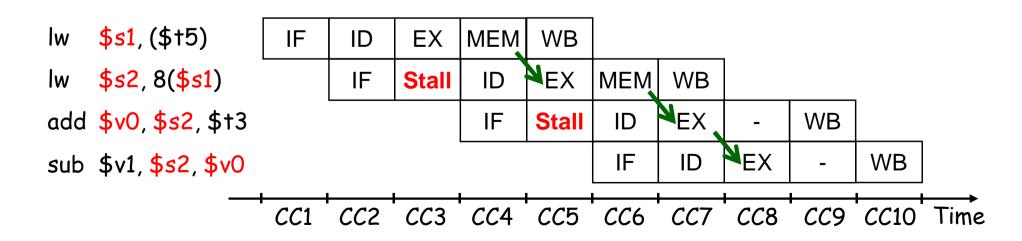

# Showing Stall Cycles

- Stall cycles can be shown on instruction-time diagram

- Hazard is detected in the Decode stage

- Stall indicates that instruction is delayed

- Instruction fetching is also delayed after a stall

- Example:

Data forwarding is shown using green arrows

# Hazard Detecting and Forwarding Logic

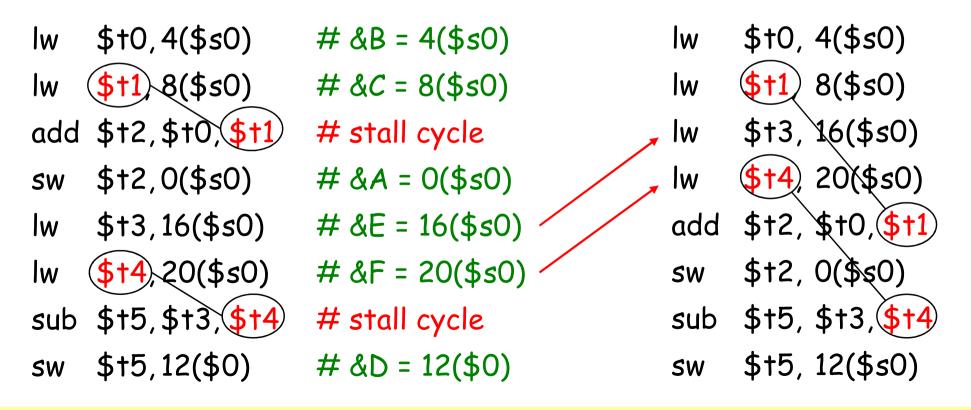

### Code Scheduling to Avoid Stalls

- Compilers reorder code in a way to avoid load stalls

- Consider the translation of the following statements:

A = B + C; D = E - F; // A thru F are in Memory

#### Slow code:

Fast code: No Stalls

### Name Dependence: Write After Read

- Instruction J should write its result after it is read by I

- Called anti-dependence by compiler writers

- I: sub \$t4, \$t1, \$t3 # \$t1 is read

- J: add \$t1, \$t2, \$t3 # \$t1 is written

- Results from reuse of the name \$t1

- ✤ NOT a data hazard in the 5-stage pipeline because:

- $\diamond$  Reads are always in stage 2

- $\diamond$  Writes are always in stage 5, and

- ♦ Instructions are processed in order

- Anti-dependence can be eliminated by renaming

- Use a different destination register for add (eg, \$t5)

### Name Dependence: Write After Write

- Same destination register is written by two instructions

- Called output-dependence in compiler terminology

- I: sub \$t1, \$t4, \$t3 # \$t1 is written

- J: add \$t1, \$t2, \$t3 # \$t1 is written again

- ✤ Not a data hazard in the 5-stage pipeline because:

- $\diamond$  All writes are ordered and always take place in stage 5

- However, can be a hazard in more complex pipelines

- ♦ If instructions are allowed to complete out of order, and

- Instruction J completes and writes \$t1 before instruction I

- Output dependence can be eliminated by renaming \$t1

- Read After Read is NOT a name dependence

Next...

Pipelined Datapath and Control

Pipeline Hazards

Data Hazards and Forwarding

Load Delay, Hazard Detection, and Stall

Control Hazards

Delayed Branch and Dynamic Branch Prediction

### Control Hazards

- Jump and Branch can cause great performance loss

- Jump instruction needs only the jump target address

- Branch instruction needs two things:

♦ Branch Result Taken or Not Taken

- ♦ Branch Target Address

- PC + 4

If Branch is NOT taken

- PC + 4 + 4 × immediate

If Branch is Taken

Jump and Branch targets are computed in the ID stage

♦ At which point a new instruction is already being fetched

♦ Jump Instruction: 1-cycle delay

♦ Branch: 2-cycle delay for branch result (taken or not taken)

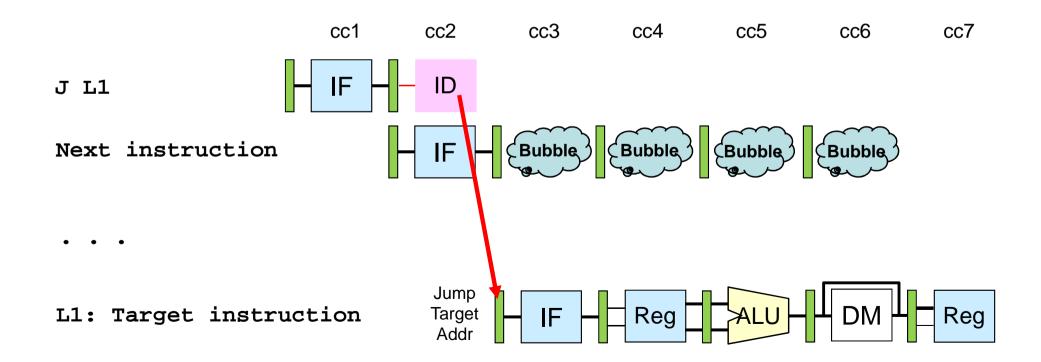

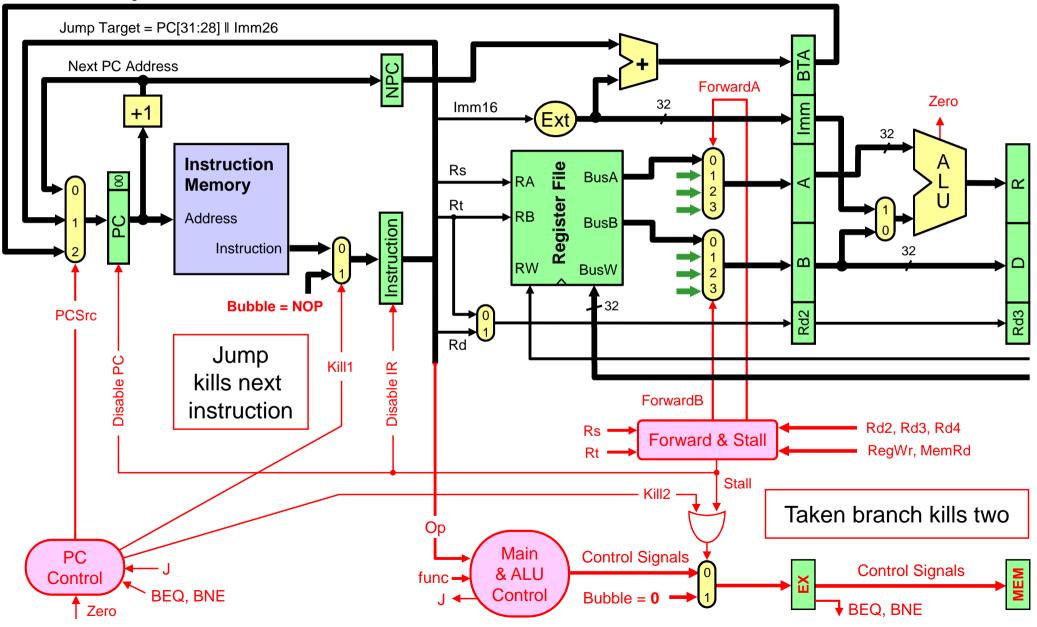

# 1-Cycle Jump Delay

- Control logic detects a Jump instruction in the 2<sup>nd</sup> Stage

- Next instruction is fetched anyway

- Convert Next instruction into bubble (Jump is always taken)

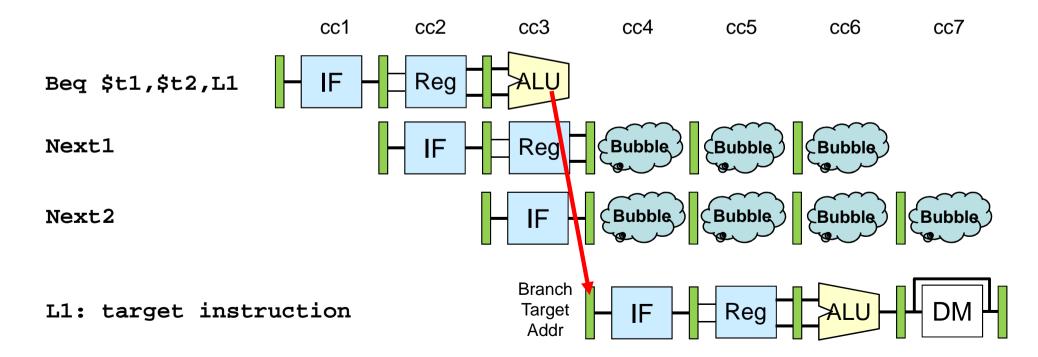

# 2-Cycle Branch Delay

- Control logic detects a Branch instruction in the 2<sup>nd</sup> Stage

- ✤ ALU computes the Branch outcome in the 3<sup>rd</sup> Stage

- Next1 and Next2 instructions will be fetched anyway

- Convert Next1 and Next2 into bubbles if branch is taken

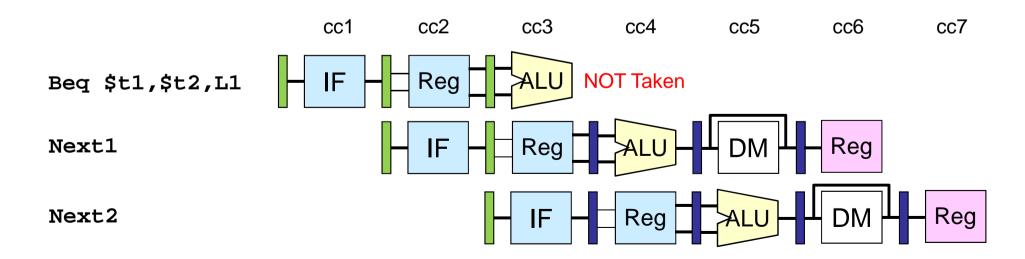

#### Predict Branch NOT Taken

- Branches can be predicted to be NOT taken

- If branch outcome is NOT taken then

- Next1 and Next2 instructions can be executed

- ♦ Do not convert Next1 & Next2 into bubbles

- ♦ No wasted cycles

## Pipelined Jump and Branch

**Branch Target Address**

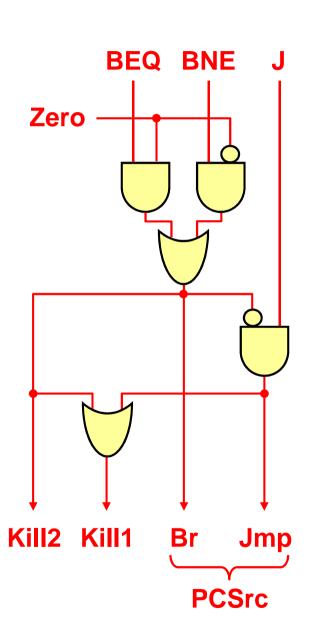

# PC Control for Pipelined Jump and Branch

- if ((BEQ && Zero) || (BNE && !Zero))

{ Jmp=0; Br=1; Kill1=1; Kill2=1; }

else if (J)

- { Jmp=1; Br=0; Kill1=1; Kill2=0; }

#### else

- { Jmp=0; Br=0; Kill1=0; Kill2=0; }

- $Br = ((BEQ \cdot Zero) + (BNE \cdot \overline{Zero}))$

- $Jmp = J \cdot \overline{Br}$

- Kill1 = J + Br

- Kill2 = Br

PCSrc = { Br, Jmp }

// 0, 1, or 2

## Jump and Branch Impact on CPI

- Base CPI = 1 without counting jump and branch

- ✤ Unconditional Jump = 5%, Conditional branch = 20%

- ✤ 90% of conditional branches are taken

- Jump kills next instruction, Taken Branch kills next two

- What is the effect of jump and branch on the CPI?

Solution:

- ✤ Jump adds 1 wasted cycle for 5% of instructions = 1 × 0.05

- ✤ Branch adds 2 wasted cycles for 20% × 90% of instructions

- $= 2 \times 0.2 \times 0.9 = 0.36$

- ✤ New CPI = 1 + 0.05 + 0.36 = 1.41 (due to wasted cycles)

Next...

Pipelined Datapath and Control

Pipeline Hazards

Data Hazards and Forwarding

Load Delay, Hazard Detection, and Stall

Control Hazards

#### Delayed Branch and Dynamic Branch Prediction

### Branch Hazard Alternatives

- Predict Branch Not Taken (previously discussed)

- ♦ Successor instruction is already fetched

- ♦ Do NOT kill instructions if the branch is NOT taken

- ♦ Kill only instructions appearing after Jump or taken branch

#### Delayed Branch

- ♦ Define branch to take place AFTER the next instruction

- ♦ Compiler/assembler fills the branch delay slot (for 1 delay cycle)

- Dynamic Branch Prediction

- ♦ Loop branches are taken most of time

- $\diamond$  Must reduce the branch delay to 0, but how?

- ♦ How to predict branch behavior at runtime?

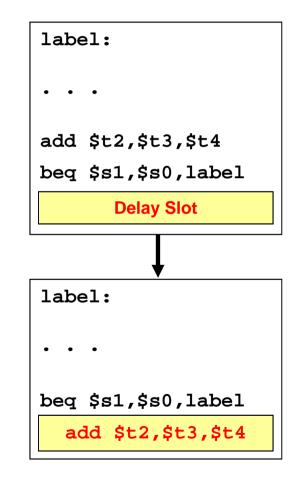

# **Delayed Branch**

- Define branch to take place after the next instruction

- MIPS defines one delay slot

- ♦ Reduces branch penalty

- Compiler fills the branch delay slot

- ♦ By selecting an independent instruction

from before the branch

$\diamond$  Must be okay to execute instruction in the

delay slot whether branch is taken or not

- If no instruction is found

- $\diamond\,$  Compiler fills delay slot with a NO-OP

# Drawback of Delayed Branching

- New meaning for branch instruction

- ♦ Branching takes place after next instruction (Not immediately!)

- Impacts software and compiler

- ♦ Compiler is responsible to fill the branch delay slot

- However, modern processors and deeply pipelined

- ♦ Branch penalty is multiple cycles in deep pipelines

- ♦ Multiple delay slots are difficult to fill with useful instructions

- MIPS used delayed branching in earlier pipelines

- ♦ However, delayed branching lost popularity in recent processors

- ♦ Dynamic branch prediction has replaced delayed branching

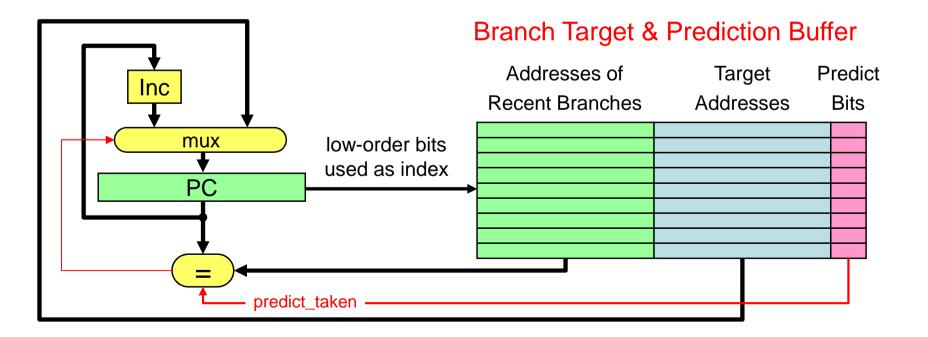

# Zero-Delayed Branching

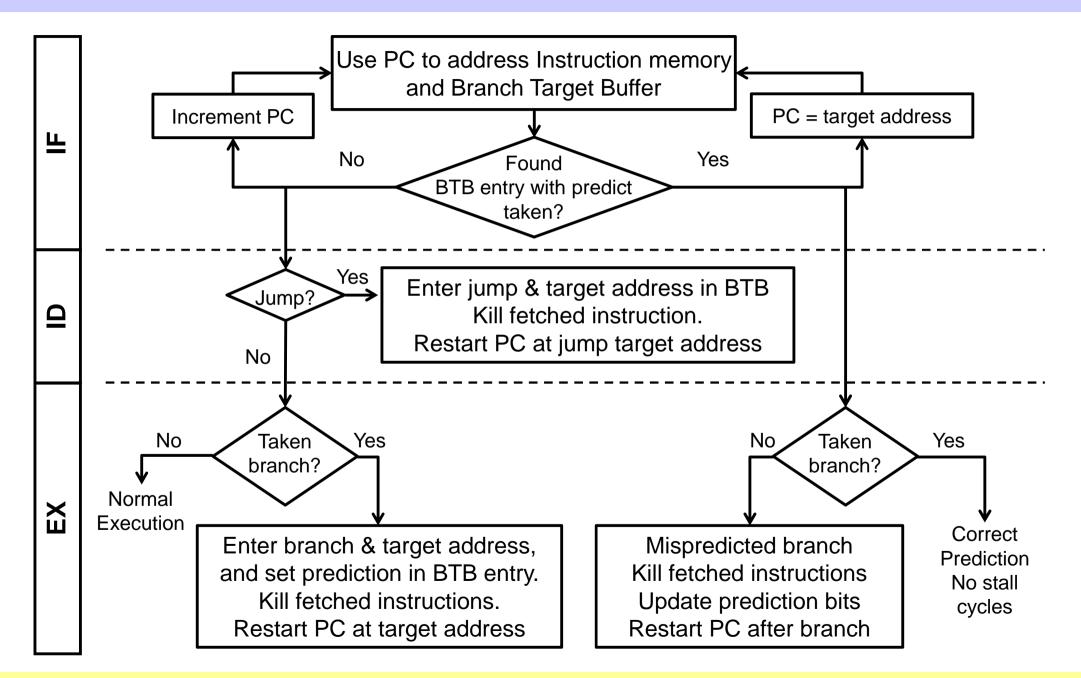

- How to achieve zero delay for a jump or a taken branch?

- ♦ Jump or branch target address is computed in the ID stage

- ♦ Next instruction has already been fetched in the IF stage

#### **Solution**

- Introduce a Branch Target Buffer (BTB) in the IF stage

- ♦ Store the target address of recent branch and jump instructions

- Use the lower bits of the PC to index the BTB

- ♦ Each BTB entry stores Branch/Jump address & Target Address

- ♦ Check the PC to see if the instruction being fetched is a branch

- ♦ Update the PC using the target address stored in the BTB

# Branch Target Buffer (IF Stage)

- The branch target buffer is implemented as a small cache

- $\diamond$  Stores the target address of recent branches and jumps

- We must also have prediction bits

- ♦ To predict whether branches are taken or not taken

- $\diamond$  The prediction bits are determined by the hardware at runtime

## Branch Target Buffer - cont'd

- Each Branch Target Buffer (BTB) entry stores:

- ♦ Address of a recent jump or branch instruction

- ♦ Target address of jump or branch

- ♦ Prediction bits for a conditional branch (Taken or Not Taken)

- To predict jump/branch target address and branch outcome before instruction is decoded and branch outcome is computed

- Use the lower bits of the PC to index the BTB

- ♦ Check if the PC matches an entry in the BTB (jump or branch)

- If there is a match and the branch is predicted to be Taken then Update the PC using the target address stored in the BTB

- The BTB entries are updated by the hardware at runtime

## **Dynamic Branch Prediction**

- Prediction of branches at runtime using prediction bits

- Prediction bits are associated with each entry in the BTB

- ♦ Prediction bits reflect the recent history of a branch instruction

- Typically few prediction bits (1 or 2) are used per entry

- We don't know if the prediction is correct or not

- ✤ If correct prediction ...

- ♦ Continue normal execution no wasted cycles

- ✤ If incorrect prediction (misprediction) ...

- $\diamond$  Kill the instructions that were incorrectly fetched  $\rightarrow$  wasted cycles

- $\diamond\,$  Update prediction bits and target address for future use

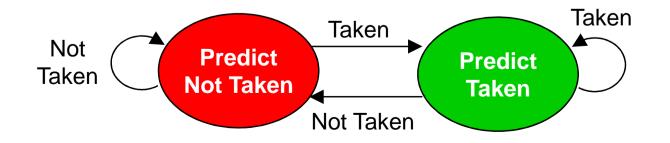

# Dynamic Branch Prediction - Cont'd

### 1-bit Prediction Scheme

- Prediction is just a hint that is assumed to be correct

- If incorrect then fetched instructions are killed

- 1-bit prediction scheme is simplest to implement

- ♦ 1 bit per branch instruction (associated with BTB entry)

- ♦ Record last outcome of a branch instruction (Taken/Not taken)

- ♦ Use last outcome to predict future behavior of a branch

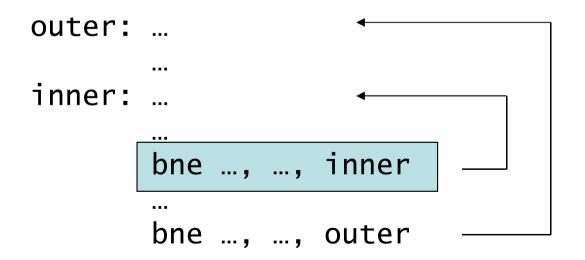

### 1-Bit Predictor: Shortcoming

Inner loop branch mispredicted twice!

- A Mispredict as taken on last iteration of inner loop

- Then mispredict as not taken on first iteration of inner loop next time around

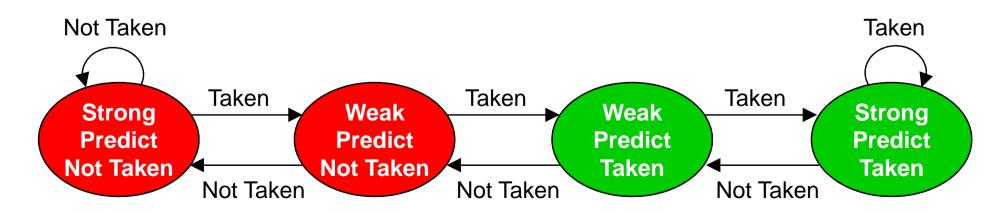

#### 2-bit Prediction Scheme

- 1-bit prediction scheme has a performance shortcoming

- 2-bit prediction scheme works better and is often used

- $\diamond$  4 states: strong and weak predict taken / predict not taken

- Implemented as a saturating counter

- $\diamond$  Counter is incremented to max=3 when branch outcome is taken

- ♦ Counter is decremented to min=0 when branch is not taken

# **Evaluating Branch Alternatives**

| Branch Scheme         | Jump               | <b>Branch Not Taken</b> | Branch Taken       |

|-----------------------|--------------------|-------------------------|--------------------|

| Predict not taken     | Penalty = 1 cycle  | Penalty = 0 cycles      | Penalty = 2 cycles |

| Delayed               | Penalty = 0 cycles | Penalty = 0 cycles      | Penalty = 1 cycle  |

| <b>BTB</b> Prediction | Penalty = 1 cycle  | Penalty = 2 cycles      | Penalty = 2 cycles |

- ✤ Assume: Jump = 2%, Branch-Not-Taken = 5%, Branch-Taken = 15%

- ✤ Assume a branch target buffer with hit rate = 90% for jump & branch

- Prediction accuracy for jump = 100%, for conditional branch = 95%

- ✤ What is the impact on the CPI? (Ideal CPI = 1 if no control hazards)

| Branch Scheme         | Jump = 2%  | Branch NT = 5%  | Branch Taken = 15%     | СРІ    |

|-----------------------|------------|-----------------|------------------------|--------|

| Predict not taken     | 0.02 × 1   | 0               | $0.15 \times 2 = 0.30$ | 1+0.32 |

| Delayed               | 0          | 0               | $0.15 \times 1 = 0.15$ | 1+0.15 |

| <b>BTB</b> Prediction | 0.02×0.1×1 | 0.05×0.9×0.05×2 | 0.15×(0.1+0.9×0.05)×2  | 1+0.05 |

## In Summary

- Three types of pipeline hazards

- ♦ Structural hazards: conflicts using a resource during same cycle

- ♦ Data hazards: caused by data dependencies between instructions

- ♦ Control hazards: caused by branch and jump instructions

- Hazards limit the performance and complicate the design

- ♦ Structural hazards: eliminated by careful design or more hardware

- ♦ Data hazards are eliminated by forwarding

- $\diamond$  However, load delay cannot be eliminated and stalls the pipeline

- ♦ Delayed branching reduces branch delay but needs compiler support

- ♦ BTB with branch prediction can reduce branch delay to zero

- ♦ Branch misprediction should kill the wrongly fetched instructions