| F.1  | Why Vector Processors?                                    | F-2  |

|------|-----------------------------------------------------------|------|

| F.2  | Basic Vector Architecture                                 | F-4  |

| F.3  | Two Real-World Issues: Vector Length and Stride           | F-16 |

| F.4  | Enhancing Vector Performance                              | F-23 |

| F.5  | Effectiveness of Compiler Vectorization                   | F-32 |

| F.6  | Putting It All Together: Performance of Vector Processors | F-34 |

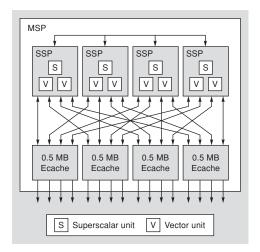

| F.7  | A Modern Vector Supercomputer: The Cray X1                | F-40 |

| F.8  | Fallacies and Pitfalls                                    | F-44 |

| F.9  | Concluding Remarks                                        | F-45 |

| F.10 | Historical Perspective and References                     | F-47 |

|      | Exercises                                                 | F-53 |

## **Vector Processors**

### Revised by Krste Asanovic Massachusetts Institute of Technology

I'm certainly not inventing vector processors. There are three kinds that I know of existing today. They are represented by the Illiac-IV, the (CDC) Star processor, and the TI (ASC) processor. Those three were all pioneering processors. . . . One of the problems of being a pioneer is you always make mistakes and I never, never want to be a pioneer. It's always best to come second when you can look at the mistakes the pioneers made.

Seymour Cray

Public lecture at Lawrence Livermore Laboratories on the introduction of the Cray-1 (1976)

## F.1 Why Vector Processors?

In Chapters 2 and 3 we saw how we could significantly increase the performance of a processor by issuing multiple instructions per clock cycle and by more deeply pipelining the execution units to allow greater exploitation of instruction-level parallelism. (This appendix assumes that you have read Chapters 2 and 3 and Appendix G completely; in addition, the discussion on vector memory systems assumes that you have read Appendix C and Chapter 5.) Unfortunately, we also saw that there are serious difficulties in exploiting ever larger degrees of ILP.

As we increase both the width of instruction issue and the depth of the machine pipelines, we also increase the number of independent instructions required to keep the processor busy with useful work. This means an increase in the number of partially executed instructions that can be in flight at one time. For a dynamically scheduled machine, hardware structures, such as instruction windows, reorder buffers, and rename register files, must grow to have sufficient capacity to hold all in-flight instructions, and worse, the number of ports on each element of these structures must grow with the issue width. The logic to track dependencies between all in-flight instructions grows quadratically in the number of instructions. Even a statically scheduled VLIW machine, which shifts more of the scheduling burden to the compiler, requires more registers, more ports per register, and more hazard interlock logic (assuming a design where hardware manages interlocks after issue time) to support more in-flight instructions, which similarly cause quadratic increases in circuit size and complexity. This rapid increase in circuit complexity makes it difficult to build machines that can control large numbers of in-flight instructions, and hence limits practical issue widths and pipeline depths.

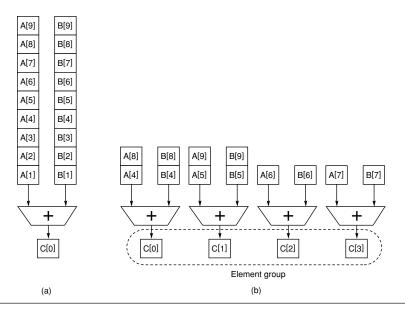

Vector processors were successfully commercialized long before instructionlevel parallel machines and take an alternative approach to controlling multiple functional units with deep pipelines. Vector processors provide high-level operations that work on vectors—linear arrays of numbers. A typical vector operation might add two 64-element, floating-point vectors to obtain a single 64-element vector result. The vector instruction is equivalent to an entire loop, with each iteration computing one of the 64 elements of the result, updating the indices, and branching back to the beginning.

Vector instructions have several important properties that solve most of the problems mentioned above:

- A single vector instruction specifies a great deal of work—it is equivalent to executing an entire loop. Each instruction represents tens or hundreds of operations, and so the instruction fetch and decode bandwidth needed to keep multiple deeply pipelined functional units busy is dramatically reduced.

- By using a vector instruction, the compiler or programmer indicates that the computation of each result in the vector is independent of the computation of other results in the same vector and so hardware does not have to check for data hazards within a vector instruction. The elements in the vector can be

computed using an array of parallel functional units, or a single very deeply pipelined functional unit, or any intermediate configuration of parallel and pipelined functional units.

- Hardware need only check for data hazards between two vector instructions once per vector operand, not once for every element within the vectors. That means the dependency checking logic required between two vector instructions is approximately the same as that required between two scalar instructions, but now many more elemental operations can be in flight for the same complexity of control logic.

- Vector instructions that access memory have a known access pattern. If the vector's elements are all adjacent, then fetching the vector from a set of heavily interleaved memory banks works very well. The high latency of initiating a main memory access versus accessing a cache is amortized, because a single access is initiated for the entire vector rather than to a single word. Thus, the cost of the latency to main memory is seen only once for the entire vector, rather than once for each word of the vector.

- Because an entire loop is replaced by a vector instruction whose behavior is predetermined, control hazards that would normally arise from the loop branch are nonexistent.

For these reasons, vector operations can be made faster than a sequence of scalar operations on the same number of data items, and designers are motivated to include vector units if the application domain can use them frequently.

Vector processors are particularly useful for large scientific and engineering applications, including car crash simulations and weather forecasting, for which a typical job might take dozens of hours of supercomputer time running over multigigabyte data sets. High-speed scalar processors rely on caches to reduce average memory access latency, but big, long-running, scientific programs often have very large active data sets that are sometimes accessed with low locality, yielding poor performance from the memory hierarchy. Some scalar architectures provide mechanisms to bypass the cache when software is aware that memory accesses will have poor locality. But saturating a modern memory system requires hardware to track hundreds or thousands of in-flight scalar memory operations, and this has been proven too costly to implement for scalar ISAs. In contrast, vector ISAs launch entire vector fetches into the memory system with each instruction, and much simpler logic can provide high sustained memory bandwidth.

When the last edition of this appendix was written in 2001, exotic vector supercomputers appeared to be slowly fading from the supercomputing arena, to be replaced by systems built from large numbers of superscalar microprocessors. But in 2002, Japan unveiled the world's fastest supercomputer, the Earth Simulator, designed to create a "virtual planet" to analyze and predict the effect of environmental changes on the world's climate. The Earth Simulator was five times faster than the previous leader, and faster than the next 12 fastest machines combined. The announcement caused a major upheaval in high-performance

computing, particularly in the United States, which was shocked to have lost the lead in an area of strategic importance. The Earth Simulator has fewer processors than competing microprocessor-based machines, but each node is a single-chip vector microprocessor with much greater efficiency on many important supercomputing codes for the reasons given above. The impact of the Earth Simulator, together with the release of a new generation of vector machines from Cray, has led to a resurgence of interest in the type of vector architectures described in this appendix.

#### F.2

### **Basic Vector Architecture**

A vector processor typically consists of an ordinary pipelined scalar unit plus a vector unit. All functional units within the vector unit have a latency of several clock cycles. This allows a shorter clock cycle time and is compatible with long-running vector operations that can be deeply pipelined without generating hazards. Most vector processors allow the vectors to be dealt with as floating-point numbers, as integers, or as logical data. Here we will focus on floating point. The scalar unit is basically no different from the type of advanced pipelined CPU discussed in Chapters 2 and 3, and commercial vector machines have included both out-of-order scalar units (NEC SX/5) and VLIW scalar units (Fujitsu VPP5000).

There are two primary types of architectures for vector processors: *vector-register processors* and *memory-memory vector processors*. In a vector-register processor, all vector operations—except load and store—are among the vector registers. These architectures are the vector counterpart of a load-store architecture. All major vector computers shipped since the late 1980s use a vector-register architecture, including the Cray Research processors (Cray-1, Cray-2, X-MP, YMP, C90, T90, SV1, and X1), the Japanese supercomputers (NEC SX/2 through SX/8, Fujitsu VP200 through VPP5000, and the Hitachi S820 and S-8300), and the minisupercomputers (Convex C-1 through C-4). In a memory-memory vector processor, all vector operations are memory to memory. The first vector computers were of this type, as were CDC's vector computers. From this point on we will focus on vector-register architectures only; we will briefly return to memory-memory vector architectures at the end of the appendix (Section F.10) to discuss why they have not been as successful as vector-register architectures.

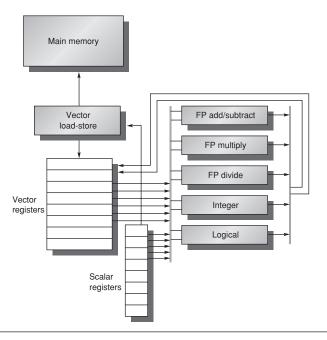

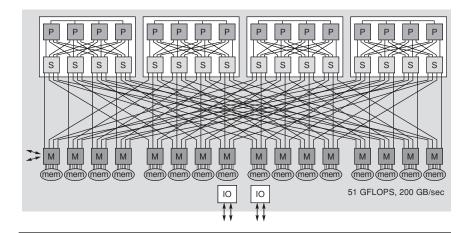

We begin with a vector-register processor consisting of the primary components shown in Figure F.1. This processor, which is loosely based on the Cray-1, is the foundation for discussion throughout most of this appendix. We will call it VMIPS; its scalar portion is MIPS, and its vector portion is the logical vector extension of MIPS. The rest of this section examines how the basic architecture of VMIPS relates to other processors.

The primary components of the instruction set architecture of VMIPS are the following:

Vector registers—Each vector register is a fixed-length bank holding a single vector. VMIPS has eight vector registers, and each vector register holds 64

**Figure F.1** The basic structure of a vector-register architecture, VMIPS. This processor has a scalar architecture just like MIPS. There are also eight 64-element vector registers, and all the functional units are vector functional units. Special vector instructions are defined both for arithmetic and for memory accesses. We show vector units for logical and integer operations. These are included so that VMIPS looks like a standard vector processor, which usually includes these units. However, we will not be discussing these units except in the exercises. The vector and scalar registers have a significant number of read and write ports to allow multiple simultaneous vector operations. These ports are connected to the inputs and outputs of the vector functional units by a set of crossbars (shown in thick gray lines). In Section F.4 we add chaining, which will require additional interconnect capability.

elements. Each vector register must have at least two read ports and one write port in VMIPS. This will allow a high degree of overlap among vector operations to different vector registers. (We do not consider the problem of a shortage of vector-register ports. In real machines this would result in a structural hazard.) The read and write ports, which total at least 16 read ports and 8 write ports, are connected to the functional unit inputs or outputs by a pair of crossbars. (The description of the vector-register file design has been simplified here. Real machines make use of the regular access pattern within a vector instruction to reduce the costs of the vector-register file circuitry [Asanovic 1998]. For example, the Cray-1 manages to implement the register file with only a single port per register.)

- Vector functional units—Each unit is fully pipelined and can start a new operation on every clock cycle. A control unit is needed to detect hazards, both from conflicts for the functional units (structural hazards) and from conflicts for register accesses (data hazards). VMIPS has five functional units, as shown in Figure F.1. For simplicity, we will focus exclusively on the floating-point functional units. Depending on the vector processor, scalar operations either use the vector functional units or use a dedicated set. We assume the functional units are shared, but again, for simplicity, we ignore potential conflicts.

- Vector load-store unit—This is a vector memory unit that loads or stores a vector to or from memory. The VMIPS vector loads and stores are fully pipelined, so that words can be moved between the vector registers and memory with a bandwidth of 1 word per clock cycle, after an initial latency. This unit would also normally handle scalar loads and stores.

- A set of scalar registers—Scalar registers can also provide data as input to the vector functional units, as well as compute addresses to pass to the vector load-store unit. These are the normal 32 general-purpose registers and 32 floating-point registers of MIPS. Scalar values are read out of the scalar register file, then latched at one input of the vector functional units.

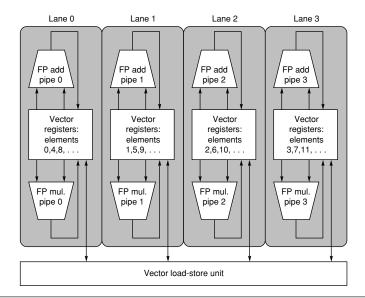

Figure F.2 shows the characteristics of some typical vector processors, including the size and count of the registers, the number and types of functional units, and the number of load-store units. The last column in Figure F.2 shows the number of *lanes* in the machine, which is the number of parallel pipelines used to execute operations within each vector instruction. Lanes are described later in Section F.4; here we assume VMIPS has only a single pipeline per vector functional unit (one lane).

In VMIPS, vector operations use the same names as MIPS operations, but with the letter "V" appended. Thus, ADDV.D is an add of two double-precision vectors. The vector instructions take as their input either a pair of vector registers (ADDV.D) or a vector register and a scalar register, designated by appending "VS" (ADDVS.D). In the latter case, the value in the scalar register is used as the input for all operations—the operation ADDVS.D will add the contents of a scalar register to each element in a vector register. The scalar value is copied over to the vector functional unit at issue time. Most vector operations have a vector destination register, although a few (population count) produce a scalar value, which is stored to a scalar register. The names LV and SV denote vector load and vector store, and they load or store an entire vector of double-precision data. One operand is the vector register to be loaded or stored; the other operand, which is a MIPS general-purpose register, is the starting address of the vector in memory. Figure F.3 lists the VMIPS vector instructions. In addition to the vector registers, we need two additional special-purpose registers: the vector-length and vectormask registers. We will discuss these registers and their purpose in Sections F.3 and F.4, respectively.

| Processor (year)                  | Vector<br>clock<br>rate<br>(MHz) | Vector<br>registers | Elements per<br>register<br>(64-bit<br>elements) | Vector arithmetic units                                                                       | Vector<br>load-store<br>units | Lanes                    |

|-----------------------------------|----------------------------------|---------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------|--------------------------|

| Cray-1 (1976)                     | 80                               | 8                   | 64                                               | 6: FP add, FP multiply, FP reciprocal, integer add, logical, shift                            | 1                             | 1                        |

| Cray X-MP (1983) Cray Y-MP (1988) | 118<br>166                       | 8                   | 64                                               | 8: FP add, FP multiply, FP reciprocal, integer add, 2 logical, shift, population count/parity | 2 loads<br>1 store            | 1                        |

| Cray-2 (1985)                     | 244                              | 8                   | 64                                               | 5: FP add, FP multiply, FP reciprocal/sqrt, integer add/shift/population count, logical       | 1                             | 1                        |

| Fujitsu VP100/<br>VP200 (1982)    | 133                              | 8–256               | 32–1024                                          | 3: FP or integer add/logical, multiply, divide                                                | 2                             | 1 (VP100)<br>2 (VP200)   |

| Hitachi S810/S820<br>(1983)       | 71                               | 32                  | 256                                              | 4: FP multiply-add, FP multiply/divide-add unit, 2 integer add/logical                        | 3 loads<br>1 store            | 1 (S810)<br>2 (S820)     |

| Convex C-1 (1985)                 | 10                               | 8                   | 128                                              | 2: FP or integer multiply/divide, add/logical                                                 | 1                             | 1 (64 bit)<br>2 (32 bit) |

| NEC SX/2 (1985)                   | 167                              | 8 + 32              | 256                                              | 4: FP multiply/divide, FP add, integer add/logical, shift                                     | 1                             | 4                        |

| Cray C90 (1991) Cray T90 (1995)   | 240<br>460                       | 8                   | 128                                              | 8: FP add, FP multiply, FP reciprocal, integer add, 2 logical, shift, population count/parity | 2 loads<br>1 store            | 2                        |

| NEC SX/5 (1998)                   | 312                              | 8 + 64              | 512                                              | 4: FP or integer add/shift, multiply, divide, logical                                         | 1                             | 16                       |

| Fujitsu VPP5000<br>(1999)         | 300                              | 8–256               | 128–4096                                         | 3: FP or integer multiply, add/logical, divide                                                | 1 load<br>1 store             | 16                       |

| Cray SV1 (1998) SV1ex (2001)      | 300<br>500                       | 8                   | 64<br>(MSP)                                      | 8: FP add, FP multiply, FP reciprocal, integer add, 2 logical, shift, population count/parity | 1 load-store<br>1 load        | 2<br>8 (MSP)             |

| VMIPS (2001)                      | 500                              | 8                   | 64                                               | 5: FP multiply, FP divide, FP add, integer add/shift, logical                                 | 1 load-store                  | 1                        |

| NEC SX/6 (2001)                   | 500                              | 8 + 64              | 256                                              | 4: FP or integer add/shift, multiply, divide, logical                                         | 1                             | 8                        |

| NEC SX/8 (2004)                   | 2000                             | 8 + 64              | 256                                              | 4: FP or integer add/shift, multiply, divide, logical                                         | 1                             | 4                        |

| Cray X1 (2002)                    | 800                              | 32                  | 64<br>256 (MSP)                                  | 3: FP or integer, add/logical, multiply/shift, divide/square root/logical                     | 1 load<br>1 store             | 2<br>8 (MSP)             |

| Cray XIE (2005)                   | 1130                             |                     |                                                  |                                                                                               |                               |                          |

**Figure F.2** Characteristics of several vector-register architectures. If the machine is a multiprocessor, the entries correspond to the characteristics of one processor. Several of the machines have different clock rates in the vector and scalar units; the clock rates shown are for the vector units. The Fujitsu machines' vector registers are configurable: The size and count of the 8K 64-bit entries may be varied inversely to one another (e.g., on the VP200, from eight registers each 1K elements long to 256 registers each 32 elements long). The NEC machines have eight foreground vector registers connected to the arithmetic units plus 32–64 background vector registers connected between the memory system and the foreground vector registers. Add pipelines perform add and subtract. The multiply/divide-add unit on the Hitachi S810/820 performs an FP multiply or divide followed by an add or subtract (while the multiply-add unit performs a multiply followed by an add or subtract). Note that most processors use the vector FP multiply and divide units for vector integer multiply and divide, and several of the processors use the same units for FP scalar and FP vector operations. Each vector load-store unit represents the ability to do an independent, overlapped transfer to or from the vector registers. The number of lanes is the number of parallel pipelines in each of the functional units as described in Section F.4. For example, the NEC SX/5 can complete 16 multiplies per cycle in the multiply functional unit. Several machines can split a 64-bit lane into two 32-bit lanes to increase performance for applications that require only reduced precision. The Cray SV1 and Cray X1 can group four CPUs with two lanes each to act in unison as a single larger CPU with eight lanes, which Cray calls a Multi-Streaming Processor (MSP).

| Instruction                  | Operands                         | Function                                                                                                                                                                                                                                                                                    |

|------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDV.D<br>ADDVS.D            | V1,V2,V3<br>V1,V2,F0             | Add elements of V2 and V3, then put each result in V1.<br>Add F0 to each element of V2, then put each result in V1.                                                                                                                                                                         |

| SUBV.D<br>SUBVS.D<br>SUBSV.D | V1,V2,V3<br>V1,V2,F0<br>V1,F0,V2 | Subtract elements of V3 from V2, then put each result in V1. Subtract F0 from elements of V2, then put each result in V1. Subtract elements of V2 from F0, then put each result in V1.                                                                                                      |

| MULV.D<br>MULVS.D            | V1,V2,V3<br>V1,V2,F0             | Multiply elements of V2 and V3, then put each result in V1.  Multiply each element of V2 by F0, then put each result in V1.                                                                                                                                                                 |

| DIVV.D<br>DIVVS.D<br>DIVSV.D | V1,V2,V3<br>V1,V2,F0<br>V1,F0,V2 | Divide elements of V2 by V3, then put each result in V1. Divide elements of V2 by F0, then put each result in V1. Divide F0 by elements of V2, then put each result in V1.                                                                                                                  |

| LV                           | V1,R1                            | Load vector register V1 from memory starting at address R1.                                                                                                                                                                                                                                 |

| SV                           | R1,V1                            | Store vector register V1 into memory starting at address R1.                                                                                                                                                                                                                                |

| LVWS                         | V1,(R1,R2)                       | Load V1 from address at R1 with stride in R2, i.e., R1+i × R2.                                                                                                                                                                                                                              |

| SVWS                         | (R1,R2),V1                       | Store V1 from address at R1 with stride in R2, i.e., R1+i × R2.                                                                                                                                                                                                                             |

| LVI                          | V1,(R1+V2)                       | Load V1 with vector whose elements are at R1+V2(i), i.e., V2 is an index.                                                                                                                                                                                                                   |

| SVI                          | (R1+V2),V1                       | Store V1 to vector whose elements are at R1+V2(i), i.e., V2 is an index.                                                                                                                                                                                                                    |

| CVI                          | V1,R1                            | Create an index vector by storing the values 0, $1 \times R1$ , $2 \times R1$ ,, $63 \times R1$ into V1.                                                                                                                                                                                    |

| SV.D<br>SVS.D                | V1,V2<br>V1,F0                   | Compare the elements (EQ, NE, GT, LT, GE, LE) in V1 and V2. If condition is true, put a 1 in the corresponding bit vector; otherwise put 0. Put resulting bit vector in vector-mask register (VM). The instruction SVS.D performs the same compare but using a scalar value as one operand. |

| POP                          | R1,VM                            | Count the 1s in the vector-mask register and store count in R1.                                                                                                                                                                                                                             |

| CVM                          |                                  | Set the vector-mask register to all 1s.                                                                                                                                                                                                                                                     |

| MTC1<br>MFC1                 | VLR,R1<br>R1,VLR                 | Move contents of R1 to the vector-length register.  Move the contents of the vector-length register to R1.                                                                                                                                                                                  |

| MVTM<br>MVFM                 | VM,F0<br>F0,VM                   | Move contents of F0 to the vector-mask register.  Move contents of vector-mask register to F0.                                                                                                                                                                                              |

**Figure F.3** The VMIPS vector instructions. Only the double-precision FP operations are shown. In addition to the vector registers, there are two special registers, VLR (discussed in Section F.3) and VM (discussed in Section F.4). These special registers are assumed to live in the MIPS coprocessor 1 space along with the FPU registers. The operations with stride are explained in Section F.3, and the uses of the index creation and indexed load-store operations are explained in Section F.4.

## **How Vector Processors Work: An Example**

A vector processor is best understood by looking at a vector loop on VMIPS. Let's take a typical vector problem, which will be used throughout this appendix:

$$Y = a \times X + Y$$

X and Y are vectors, initially resident in memory, and a is a scalar. This is the so-called SAXPY or DAXPY loop that forms the inner loop of the Linpack benchmark. (SAXPY stands for single-precision  $\underline{a} \times \underline{X}$  plus  $\underline{Y}$ ; DAXPY for double-

precision  $\underline{a} \times \underline{X}$  plus  $\underline{Y}$ .) Linpack is a collection of linear algebra routines, and the routines for performing Gaussian elimination constitute what is known as the Linpack benchmark. The DAXPY routine, which implements the preceding loop, represents a small fraction of the source code of the Linpack benchmark, but it accounts for most of the execution time for the benchmark.

For now, let us assume that the number of elements, or length, of a vector register (64) matches the length of the vector operation we are interested in. (This restriction will be lifted shortly.)

## **Example** Show the code for MIPS and VMIPS for the DAXPY loop. Assume that the starting addresses of X and Y are in Rx and Ry, respectively.

**Answer** Here is the MIPS code.

```

L.D

FO, a

;load scalar a

DADDIU

R4, Rx, #512

; last address to load

Loop:

L.D

F2,0(Rx)

;load X(i)

MUL, D

F2, F2, F0

; a \times X(i)

L.D

F4,0(Ry)

;load Y(i)

ADD.D

F4, F4, F2

; a \times X(i) + Y(i)

S.D

0(Ry),F4

;store into Y(i)

DADDIU

Rx,Rx,#8

;increment index to X

DADDIU

Ry, Ry, #8

;increment index to Y

DSUBU

R20, R4, Rx

compute bound

BNEZ

R20, Loop

;check if done

```

Here is the VMIPS code for DAXPY.

| L.D     | FO,a     | ;load scalar a          |

|---------|----------|-------------------------|

| LV      | V1,Rx    | ;load vector X          |

| MULVS.D | V2,V1,F0 | ;vector-scalar multiply |

| LV      | V3,Ry    | ;load vector Y          |

| ADDV.D  | V4,V2,V3 | ;add                    |

| SV      | Ry,V4    | ;store the result       |

There are some interesting comparisons between the two code segments in this example. The most dramatic is that the vector processor greatly reduces the dynamic instruction bandwidth, executing only 6 instructions versus almost 600 for MIPS. This reduction occurs both because the vector operations work on 64 elements and because the overhead instructions that constitute nearly half the loop on MIPS are not present in the VMIPS code.

Another important difference is the frequency of pipeline interlocks. In the straightforward MIPS code every ADD.D must wait for a MUL.D, and every S.D must wait for the ADD.D. On the vector processor, each vector instruction will only stall for the first element in each vector, and then subsequent elements will

flow smoothly down the pipeline. Thus, pipeline stalls are required only once per vector operation, rather than once per vector element. In this example, the pipeline stall frequency on MIPS will be about 64 times higher than it is on VMIPS. The pipeline stalls can be eliminated on MIPS by using software pipelining or loop unrolling (as described in Appendix G). However, the large difference in instruction bandwidth cannot be reduced.

#### **Vector Execution Time**

The execution time of a sequence of vector operations primarily depends on three factors: the length of the operand vectors, structural hazards among the operations, and the data dependences. Given the vector length and the *initiation rate*, which is the rate at which a vector unit consumes new operands and produces new results, we can compute the time for a single vector instruction. All modern supercomputers have vector functional units with multiple parallel pipelines (or lanes) that can produce two or more results per clock cycle, but may also have some functional units that are not fully pipelined. For simplicity, our VMIPS implementation has one lane with an initiation rate of one element per clock cycle for individual operations. Thus, the execution time for a single vector instruction is approximately the vector length.

To simplify the discussion of vector execution and its timing, we will use the notion of a convoy, which is the set of vector instructions that could potentially begin execution together in one clock period. (Although the concept of a convoy is used in vector compilers, no standard terminology exists. Hence, we created the term *convoy*.) The instructions in a convoy *must not* contain any structural or data hazards (though we will relax this later); if such hazards were present, the instructions in the potential convoy would need to be serialized and initiated in different convoys. Placing vector instructions into a convoy is analogous to placing scalar operations into a VLIW instruction. To keep the analysis simple, we assume that a convoy of instructions must complete execution before any other instructions (scalar or vector) can begin execution. We will relax this in Section F.4 by using a less restrictive, but more complex, method for issuing instructions.

Accompanying the notion of a convoy is a timing metric, called a *chime*, that can be used for estimating the performance of a vector sequence consisting of convoys. A chime is the unit of time taken to execute one convoy. A chime is an approximate measure of execution time for a vector sequence; a chime measurement is independent of vector length. Thus, a vector sequence that consists of m convoys executes in m chimes, and for a vector length of n, this is approximately  $m \times n$  clock cycles. A chime approximation ignores some processor-specific overheads, many of which are dependent on vector length. Hence, measuring time in chimes is a better approximation for long vectors. We will use the chime measurement, rather than clock cycles per result, to explicitly indicate that certain overheads are being ignored.

If we know the number of convoys in a vector sequence, we know the execution time in chimes. One source of overhead ignored in measuring chimes is any limitation on initiating multiple vector instructions in a clock cycle. If only one vector instruction can be initiated in a clock cycle (the reality in most vector processors), the chime count will underestimate the actual execution time of a convoy. Because the vector length is typically much greater than the number of instructions in the convoy, we will simply assume that the convoy executes in one chime.

#### Example

Show how the following code sequence lays out in convoys, assuming a single copy of each vector functional unit:

```

L۷

;load vector X

V1,Rx

MULVS.D

V2, V1, F0

;vector-scalar multiply

L۷

V3, Ry

;load vector Y

ADDV.D

V4, V2, V3

; add

Ry, V4

store the result

```

How many chimes will this vector sequence take? How many cycles per FLOP (floating-point operation) are needed, ignoring vector instruction issue overhead?

#### Answer

The first convoy is occupied by the first LV instruction. The MULVS.D is dependent on the first LV, so it cannot be in the same convoy. The second LV instruction can be in the same convoy as the MULVS.D. The ADDV.D is dependent on the second LV, so it must come in yet a third convoy, and finally the SV depends on the ADDV.D, so it must go in a following convoy. This leads to the following layout of vector instructions into convoys:

- LV

- MULVS.D LV

- ADDV.D

- SV

The sequence requires four convoys and hence takes four chimes. Since the sequence takes a total of four chimes and there are two floating-point operations per result, the number of cycles per FLOP is 2 (ignoring any vector instruction issue overhead). Note that although we allow the MULVS.D and the LV both to execute in convoy 2, most vector machines will take 2 clock cycles to initiate the instructions.

The chime approximation is reasonably accurate for long vectors. For example, for 64-element vectors, the time in chimes is four, so the sequence would take about 256 clock cycles. The overhead of issuing convoy 2 in two separate clocks would be small.

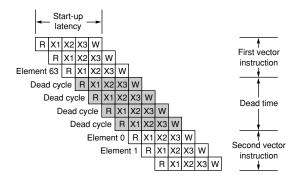

Another source of overhead is far more significant than the issue limitation. The most important source of overhead ignored by the chime model is vector start-up time. The start-up time comes from the pipelining latency of the vector operation and is principally determined by how deep the pipeline is for the functional unit used. The start-up time increases the effective time to execute a convoy to more than one chime. Because of our assumption that convoys do not overlap in time, the start-up time delays the execution of subsequent convoys. Of course the instructions in successive convoys have either structural conflicts for some functional unit or are data dependent, so the assumption of no overlap is reasonable. The actual time to complete a convoy is determined by the sum of the vector length and the start-up time. If vector lengths were infinite, this start-up overhead would be amortized, but finite vector lengths expose it, as the following example shows.

#### **Example** Assume the start-up overhead for functional units is shown in Figure F.4.

Show the time that each convoy can begin and the total number of cycles needed. How does the time compare to the chime approximation for a vector of length 64?

#### Answer

Figure F.5 provides the answer in convoys, assuming that the vector length is *n*. One tricky question is when we assume the vector sequence is done; this determines whether the start-up time of the SV is visible or not. We assume that the instructions following cannot fit in the same convoy, and we have already assumed that convoys do not overlap. Thus the total time is given by the time until the last vector instruction in the last convoy completes. This is an approximation, and the start-up time of the last vector instruction may be seen in some sequences and not in others. For simplicity, we always include it.

The time per result for a vector of length 64 is 4 + (42/64) = 4.65 clock cycles, while the chime approximation would be 4. The execution time with start-up overhead is 1.16 times higher.

For simplicity, we will use the chime approximation for running time, incorporating start-up time effects only when we want more detailed performance or to illustrate the benefits of some enhancement. For long vectors, a typical situation, the overhead effect is not that large. Later in the appendix we will explore ways to reduce start-up overhead.

Start-up time for an instruction comes from the pipeline depth for the functional unit implementing that instruction. If the initiation rate is to be kept at 1 clock cycle per result, then

Pipeline depth =

$$\left[ \frac{\text{Total functional unit time}}{\text{Clock cycle time}} \right]$$

For example, if an operation takes 10 clock cycles, it must be pipelined 10 deep to achieve an initiation rate of one per clock cycle. Pipeline depth, then, is determined by the complexity of the operation and the clock cycle time of the processor. The pipeline depths of functional units vary widely—from 2 to 20 stages is not uncommon—although the most heavily used units have pipeline depths of 4–8 clock cycles.

| Unit                | Start-up overhead (cycles) |

|---------------------|----------------------------|

| Load and store unit | 12                         |

| Multiply unit       | 7                          |

| Add unit            | 6                          |

Figure F.4 Start-up overhead.

| Convoy        | Starting time | First-result time | Last-result time |

|---------------|---------------|-------------------|------------------|

| 1. LV         | 0             | 12                | 11 + n           |

| 2. MULVS.D LV | 12 + n        | 12 + n + 12       | 23 + 2n          |

| 3. ADDV.D     | 24 + 2n       | 24 + 2n + 6       | 29 + 3n          |

| 4. SV         | 30 + 3n       | 30 + 3n + 12      | 41 + 4n          |

Figure F.5 Starting times and first- and last-result times for convoys 1 through 4. The vector length is n.

| Operation       | Start-up penalty |

|-----------------|------------------|

| Vector add      | 6                |

| Vector multiply | 7                |

| Vector divide   | 20               |

| Vector load     | 12               |

Figure F.6 Start-up penalties on VMIPS. These are the start-up penalties in clock cycles for VMIPS vector operations.

For VMIPS, we will use the same pipeline depths as the Cray-1, although latencies in more modern processors have tended to increase, especially for loads. All functional units are fully pipelined. As shown in Figure F.6, pipeline depths are 6 clock cycles for floating-point add and 7 clock cycles for floatingpoint multiply. On VMIPS, as on most vector processors, independent vector operations using different functional units can issue in the same convoy.

## Vector Load-Store Units and Vector Memory Systems

The behavior of the load-store vector unit is significantly more complicated than that of the arithmetic functional units. The start-up time for a load is the time to get the first word from memory into a register. If the rest of the vector can be supplied without stalling, then the vector initiation rate is equal to the rate at which new words are fetched or stored. Unlike simpler functional units, the initiation rate may not necessarily be 1 clock cycle because memory bank stalls can reduce effective throughput.

Typically, penalties for start-ups on load-store units are higher than those for arithmetic functional units—over 100 clock cycles on some processors. For VMIPS we assume a start-up time of 12 clock cycles, the same as the Cray-1. Figure F.6 summarizes the start-up penalties for VMIPS vector operations.

To maintain an initiation rate of 1 word fetched or stored per clock, the memory system must be capable of producing or accepting this much data. This is usually done by spreading accesses across multiple independent memory banks. As we will see in the next section, having significant numbers of banks is useful for dealing with vector loads or stores that access rows or columns of data.

Most vector processors use memory banks rather than simple interleaving for three primary reasons:

- 1. Many vector computers support multiple loads or stores per clock, and the memory bank cycle time is often several times larger than the CPU cycle time. To support multiple simultaneous accesses, the memory system needs to have multiple banks and be able to control the addresses to the banks independently.

- 2. As we will see in the next section, many vector processors support the ability to load or store data words that are not sequential. In such cases, independent bank addressing, rather than interleaving, is required.

- 3. Many vector computers support multiple processors sharing the same memory system, and so each processor will be generating its own independent stream of addresses.

In combination, these features lead to a large number of independent memory banks, as shown by the following example.

#### Example

The Cray T90 has a CPU clock period of 2.167 ns and in its largest configuration (Cray T932) has 32 processors, each capable of generating four loads and two stores per cycle. The CPU clock cycle is 2.167 ns, while the cycle time of the SRAMs used in the memory system is 15 ns. Calculate the minimum number of memory banks required to allow all CPUs to run at full memory bandwidth.

#### Answer

The maximum number of memory references each cycle is 192 (32 CPUs times 6 references per CPU). Each SRAM bank is busy for 15/2.167 = 6.92 clock cycles, which we round up to 7 CPU clock cycles. Therefore we require a minimum of  $192 \times 7 = 1344$  memory banks!

The Cray T932 actually has 1024 memory banks, and so the early models could not sustain full bandwidth to all CPUs simultaneously. A subsequent memory upgrade replaced the 15 ns asynchronous SRAMs with pipelined synchronous SRAMs that more than halved the memory cycle time, thereby providing sufficient bandwidth.

The desired access rate and the bank access time determined how many banks were needed to access memory without stalls. The next example shows how these timings work out in a vector processor.

#### Example

Suppose we want to fetch a vector of 64 elements starting at byte address 136, and a memory access takes 6 clocks. How many memory banks must we have to support one fetch per clock cycle? With what addresses are the banks accessed? When will the various elements arrive at the CPU?

#### Answer

Six clocks per access require at least six banks, but because we want the number of banks to be a power of two, we choose to have eight banks. Figure F.7 shows the timing for the first few sets of accesses for an eight-bank system with a 6clock-cycle access latency.

|           |      |      |      | Bank |      |      |      |      |

|-----------|------|------|------|------|------|------|------|------|

| Cycle no. | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

| 0         |      | 136  |      |      |      |      |      |      |

| 1         |      | busy | 144  |      |      |      |      |      |

| 2         |      | busy | busy | 152  |      |      |      |      |

| 3         |      | busy | busy | busy | 160  |      |      |      |

| 4         |      | busy | busy | busy | busy | 168  |      |      |

| 5         |      | busy | busy | busy | busy | busy | 176  |      |

| 6         |      |      | busy | busy | busy | busy | busy | 184  |

| 7         | 192  |      |      | busy | busy | busy | busy | busy |

| 8         | busy | 200  |      |      | busy | busy | busy | busy |

| 9         | busy | busy | 208  |      |      | busy | busy | busy |

| 10        | busy | busy | busy | 216  |      |      | busy | busy |

| 11        | busy | busy | busy | busy | 224  |      |      | busy |

| 12        | busy | busy | busy | busy | busy | 232  |      |      |

| 13        |      | busy | busy | busy | busy | busy | 240  |      |

| 14        |      |      | busy | busy | busy | busy | busy | 248  |

| 15        | 256  |      |      | busy | busy | busy | busy | busy |

| 16        | busy | 264  |      |      | busy | busy | busy | busy |

Figure F.7 Memory addresses (in bytes) by bank number and time slot at which access begins. Each memory bank latches the element address at the start of an access and is then busy for 6 clock cycles before returning a value to the CPU. Note that the CPU cannot keep all eight banks busy all the time because it is limited to supplying one new address and receiving one data item each cycle.

F.3

The timing of real memory banks is usually split into two different components, the access latency and the bank cycle time (or bank busy time). The access latency is the time from when the address arrives at the bank until the bank returns a data value, while the busy time is the time the bank is occupied with one request. The access latency adds to the start-up cost of fetching a vector from memory (the total memory latency also includes time to traverse the pipelined interconnection networks that transfer addresses and data between the CPU and memory banks). The bank busy time governs the effective bandwidth of a memory system because a processor cannot issue a second request to the same bank until the bank busy time has elapsed.

For simple unpipelined SRAM banks as used in the previous examples, the access latency and busy time are approximately the same. For a pipelined SRAM bank, however, the access latency is larger than the busy time because each element access only occupies one stage in the memory bank pipeline. For a DRAM bank, the access latency is usually shorter than the busy time because a DRAM needs extra time to restore the read value after the destructive read operation. For memory systems that support multiple simultaneous vector accesses or allow nonsequential accesses in vector loads or stores, the number of memory banks should be larger than the minimum; otherwise, memory bank conflicts will exist. We explore this in more detail in the next section.

## Two Real-World Issues: Vector Length and Stride

This section deals with two issues that arise in real programs: What do you do when the vector length in a program is not exactly 64? How do you deal with nonadjacent elements in vectors that reside in memory? First, let's consider the issue of vector length.

## Vector-Length Control

A vector-register processor has a natural vector length determined by the number of elements in each vector register. This length, which is 64 for VMIPS, is unlikely to match the real vector length in a program. Moreover, in a real program the length of a particular vector operation is often unknown at compile time. In fact, a single piece of code may require different vector lengths. For example, consider this code:

The size of all the vector operations depends on n, which may not even be known until run time! The value of n might also be a parameter to a procedure containing the above loop and therefore be subject to change during execution.

The solution to these problems is to create a vector-length register (VLR). The VLR controls the length of any vector operation, including a vector load or store. The value in the VLR, however, cannot be greater than the length of the vector registers. This solves our problem as long as the real length is less than or equal to the *maximum vector length* (MVL) defined by the processor.

What if the value of n is not known at compile time, and thus may be greater than MVL? To tackle the second problem where the vector is longer than the maximum length, a technique called *strip mining* is used. Strip mining is the generation of code such that each vector operation is done for a size less than or equal to the MVL. We could strip-mine the loop in the same manner that we unrolled loops in Appendix G: create one loop that handles any number of iterations that is a multiple of MVL and another loop that handles any remaining iterations, which must be less than MVL. In practice, compilers usually create a single strip-mined loop that is parameterized to handle both portions by changing the length. The strip-mined version of the DAXPY loop written in FORTRAN, the major language used for scientific applications, is shown with C-style comments:

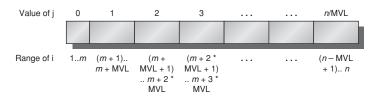

The term n/MVL represents truncating integer division (which is what FOR-TRAN does) and is used throughout this section. The effect of this loop is to block the vector into segments that are then processed by the inner loop. The length of the first segment is (n mod MVL), and all subsequent segments are of length MVL. This is depicted in Figure F.8.

The inner loop of the preceding code is vectorizable with length VL, which is equal to either (n mod MVL) or MVL. The VLR register must be set twice—once at each place where the variable VL in the code is assigned. With multiple vector operations executing in parallel, the hardware must copy the value of VLR to the

**Figure F.8** A vector of arbitrary length processed with strip mining. All blocks but the first are of length MVL, utilizing the full power of the vector processor. In this figure, the variable m is used for the expression (n mod MVL).

vector functional unit when a vector operation issues, in case VLR is changed for a subsequent vector operation.

Several vector ISAs have been developed that allow implementations to have different maximum vector-register lengths. For example, the IBM vector extension for the IBM 370 series mainframes supports an MVL of anywhere between 8 and 512 elements. A "load vector count and update" (VLVCU) instruction is provided to control strip-mined loops. The VLVCU instruction has a single scalar register operand that specifies the desired vector length. The vector-length register is set to the minimum of the desired length and the maximum available vector length, and this value is also subtracted from the scalar register, setting the condition codes to indicate if the loop should be terminated. In this way, object code can be moved unchanged between two different implementations while making full use of the available vector-register length within each strip-mined loop iteration.

In addition to the start-up overhead, we need to account for the overhead of executing the strip-mined loop. This strip-mining overhead, which arises from the need to reinitiate the vector sequence and set the VLR, effectively adds to the vector start-up time, assuming that a convoy does not overlap with other instructions. If that overhead for a convoy is 10 cycles, then the effective overhead per 64 elements increases by 10 cycles, or 0.15 cycles per element.

There are two key factors that contribute to the running time of a strip-mined loop consisting of a sequence of convoys:

- The number of convoys in the loop, which determines the number of chimes.

We use the notation T<sub>chime</sub> for the execution time in chimes.

- The overhead for each strip-mined sequence of convoys. This overhead consists of the cost of executing the scalar code for strip-mining each block, T<sub>loop</sub>, plus the vector start-up cost for each convoy, T<sub>start</sub>.

There may also be a fixed overhead associated with setting up the vector sequence the first time. In recent vector processors this overhead has become quite small, so we ignore it.

The components can be used to state the total running time for a vector sequence operating on a vector of length n, which we will call  $T_n$ :

$$T_n = \left\lceil \frac{n}{MVL} \right\rceil \times (T_{loop} + T_{start}) + n \times T_{chime}$$

The values of  $T_{\text{start}}$ ,  $T_{\text{loop}}$ , and  $T_{\text{chime}}$  are compiler and processor dependent. The register allocation and scheduling of the instructions affect both what goes in a convoy and the start-up overhead of each convoy.

For simplicity, we will use a constant value for  $T_{loop}$  on VMIPS. Based on a variety of measurements of Cray-1 vector execution, the value chosen is 15 for  $T_{loop}$ . At first glance, you might think that this value is too small. The overhead in each loop requires setting up the vector starting addresses and the strides, incrementing counters, and executing a loop branch. In practice, these scalar instruc-

tions can be totally or partially overlapped with the vector instructions, minimizing the time spent on these overhead functions. The value of  $T_{loop}$  of course depends on the loop structure, but the dependence is slight compared with the connection between the vector code and the values of  $T_{chime}$  and  $T_{start}$ .

#### Example

What is the execution time on VMIPS for the vector operation  $A = B \times s$ , where s is a scalar and the length of the vectors A and B is 200?

#### Answer

Assume the addresses of A and B are initially in Ra and Rb, s is in Fs, and recall that for MIPS (and VMIPS) R0 always holds 0. Since (200 mod 64) = 8, the first iteration of the strip-mined loop will execute for a vector length of 8 elements, and the following iterations will execute for a vector length of 64 elements. The starting byte addresses of the next segment of each vector is eight times the vector length. Since the vector length is either 8 or 64, we increment the address registers by  $8 \times 8 = 64$  after the first segment and  $8 \times 64 = 512$  for later segments. The total number of bytes in the vector is  $8 \times 200 = 1600$ , and we test for completion by comparing the address of the next vector segment to the initial address plus 1600. Here is the actual code:

|       | DADDUI  | R2,R0,#1600 | <pre>;total # bytes in vector</pre> |

|-------|---------|-------------|-------------------------------------|

|       | DADDU   | R2,R2,Ra    | ;address of the end of A vector     |

|       | DADDUI  | R1,R0,#8    | ;loads length of 1st segment        |

|       | MTC1    | VLR,R1      | ;load vector length in VLR          |

|       | DADDUI  | R1,R0,#64   | ;length in bytes of 1st segment     |

|       | DADDUI  | R3,R0,#64   | ;vector length of other segments    |

| Loop: | LV      | V1,Rb       | ;load B                             |

|       | MULVS.D | V2,V1,Fs    | ;vector * scalar                    |

|       | SV      | Ra,V2       | ;store A                            |

|       | DADDU   | Ra,Ra,R1    | ;address of next segment of A       |

|       | DADDU   | Rb,Rb,R1    | ;address of next segment of B       |

|       | DADDUI  | R1,R0,#512  | ;load byte offset next segment      |

|       | MTC1    | VLR,R3      | ;set length to 64 elements          |

|       | DSUBU   | R4,R2,Ra    | ;at the end of A?                   |

|       | BNEZ    | R4,Loop     | ;if not, go back                    |

The three vector instructions in the loop are dependent and must go into three convoys, hence  $T_{chime} = 3$ . Let's use our basic formula:

$$T_n = \left[\frac{n}{\text{MVL}}\right] \times (T_{\text{loop}} + T_{\text{start}}) + n \times T_{\text{chime}}$$

$$T_{200} = 4 \times (15 + T_{\text{start}}) + 200 \times 3$$

$$T_{200} = 60 + (4 \times T_{\text{start}}) + 600 = 660 + (4 \times T_{\text{start}})$$

The value of T<sub>start</sub> is the sum of

- the vector load start-up of 12 clock cycles

- a 7-clock-cycle start-up for the multiply

- a 12-clock-cycle start-up for the store

Thus, the value of T<sub>start</sub> is given by

$$T_{\text{start}} = 12 + 7 + 12 = 31$$

So, the overall value becomes

$$T_{200} = 660 + 4 \times 31 = 784$$

The execution time per element with all start-up costs is then 784/200 = 3.9, compared with a chime approximation of three. In Section F.4, we will be more ambitious—allowing overlapping of separate convoys.

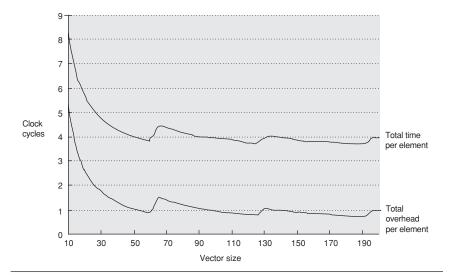

Figure F.9 shows the overhead and effective rates per element for the previous example ( $A = B \times s$ ) with various vector lengths. A chime counting model would lead to 3 clock cycles per element, while the two sources of overhead add 0.9 clock cycles per element in the limit.

Figure F.9 The total execution time per element and the total overhead time per element versus the vector length for the example on page F-19. For short vectors the total start-up time is more than one-half of the total time, while for long vectors it reduces to about one-third of the total time. The sudden jumps occur when the vector length crosses a multiple of 64, forcing another iteration of the strip-mining code and execution of a set of vector instructions. These operations increase  $T_n$  by  $T_{loop} + T_{start}$ .

The next few sections introduce enhancements that reduce this time. We will see how to reduce the number of convoys and hence the number of chimes using a technique called *chaining*. The loop overhead can be reduced by further overlapping the execution of vector and scalar instructions, allowing the scalar loop overhead in one iteration to be executed while the vector instructions in the previous instruction are completing. Finally, the vector start-up overhead can also be eliminated, using a technique that allows overlap of vector instructions in separate convoys.

#### Vector Stride

The second problem this section addresses is that the position in memory of adjacent elements in a vector may not be sequential. Consider the straightforward code for matrix multiply:

```

do 10 i = 1,100

do 10 \text{ j} = 1,100

A(i,j) = 0.0

do 10 k = 1,100

A(i,j) = A(i,j) + B(i,k) * C(k,j)

10

```

At the statement labeled 10 we could vectorize the multiplication of each row of B with each column of C and strip-mine the inner loop with k as the index variable.

To do so, we must consider how adjacent elements in B and adjacent elements in C are addressed. When an array is allocated memory, it is linearized and must be laid out in either row-major or column-major order. This linearization means that either the elements in the row or the elements in the column are not adjacent in memory. For example, if the preceding loop were written in FORTRAN, which allocates column-major order, the elements of B that are accessed by iterations in the inner loop are separated by the row size times 8 (the number of bytes per entry) for a total of 800 bytes. In Chapter 5, we saw that blocking could be used to improve the locality in cache-based systems. For vector processors without caches, we need another technique to fetch elements of a vector that are not adjacent in memory.

This distance separating elements that are to be gathered into a single register is called the stride. In the current example, using column-major layout for the matrices means that matrix C has a stride of 1, or 1 double word (8 bytes), separating successive elements, and matrix B has a stride of 100, or 100 double words (800 bytes).

Once a vector is loaded into a vector register it acts as if it had logically adjacent elements. Thus a vector-register processor can handle strides greater than one, called *nonunit strides*, using only vector-load and vector-store operations with stride capability. This ability to access nonsequential memory locations and to reshape them into a dense structure is one of the major advantages of a vector processor over a cache-based processor. Caches inherently deal with unit stride data, so that while increasing block size can help reduce miss rates for large scientific data sets with unit stride, increasing block size can have a negative effect for data that is accessed with nonunit stride. While blocking techniques can solve some of these problems (see Section 5.2), the ability to efficiently access data that is not contiguous remains an advantage for vector processors on certain problems.

On VMIPS, where the addressable unit is a byte, the stride for our example would be 800. The value must be computed dynamically, since the size of the matrix may not be known at compile time, or—just like vector length—may change for different executions of the same statement. The vector stride, like the vector starting address, can be put in a general-purpose register. Then the VMIPS instruction LVWS (load vector with stride) can be used to fetch the vector into a vector register. Likewise, when a nonunit stride vector is being stored, SVWS (store vector with stride) can be used. In some vector processors the loads and stores always have a stride value stored in a register, so that only a single load and a single store instruction are required. Unit strides occur much more frequently than other strides and can benefit from special case handling in the memory system, and so are often separated from nonunit stride operations as in VMIPS.

Complications in the memory system can occur from supporting strides greater than one. In our earlier example, we saw that unit stride memory accesses could proceed at full speed if the number of memory banks was at least as large as the bank busy time in clock cycles. Once nonunit strides are introduced, however, it becomes possible to request accesses from the same bank more frequently than the bank busy time allows. When multiple accesses contend for a bank, a memory bank conflict occurs and one access must be stalled. A bank conflict, and hence a stall, will occur if

#### Example

Suppose we have 8 memory banks with a bank busy time of 6 clocks and a total memory latency of 12 cycles. How long will it take to complete a 64-element vector load with a stride of 1? With a stride of 32?

#### Answer

Since the number of banks is larger than the bank busy time, for a stride of 1, the load will take 12 + 64 = 76 clock cycles, or 1.2 clocks per element. The worst possible stride is a value that is a multiple of the number of memory banks, as in this case with a stride of 32 and 8 memory banks. Every access to memory (after the first one) will collide with the previous access and will have to wait for the 6-clock-cycle bank busy time. The total time will be 12 + 1 + 6 \* 63 = 391 clock cycles, or 6.1 clocks per element.

Memory bank conflicts will not occur within a single vector memory instruction if the stride and number of banks are relatively prime with respect to each other and there are enough banks to avoid conflicts in the unit stride case. When there are no bank conflicts, multiword and unit strides run at the same rates. Increasing the number of memory banks to a number greater than the minimum to prevent stalls with a stride of length 1 will decrease the stall frequency for some other strides. For example, with 64 banks, a stride of 32 will stall on every other access, rather than every access. If we originally had a stride of 8 and 16 banks, every other access would stall; with 64 banks, a stride of 8 will stall on every eighth access. If we have multiple memory pipelines and/or multiple processors sharing the same memory system, we will also need more banks to prevent conflicts. Even machines with a single memory pipeline can experience memory bank conflicts on unit stride accesses between the last few elements of one instruction and the first few elements of the next instruction and increasing the number of banks will reduce the probability of these inter-instruction conflicts. In 2006, most vector supercomputers spread the accesses from each CPU across hundreds of memory banks. Because bank conflicts can still occur in nonunit stride cases, programmers favor unit stride accesses whenever possible.

A modern supercomputer may have dozens of CPUs, each with multiple memory pipelines connected to thousands of memory banks. It would be impractical to provide a dedicated path between each memory pipeline and each memory bank, and so typically a multistage switching network is used to connect memory pipelines to memory banks. Congestion can arise in this switching network as different vector accesses contend for the same circuit paths, causing additional stalls in the memory system.

## F.4 Enhancing Vector Performance

In this section we present five techniques for improving the performance of a vector processor. The first, *chaining*, deals with making a sequence of dependent vector operations run faster, and originated in the Cray-1 but is now supported on most vector processors. The next two deal with expanding the class of loops that can be run in vector mode by combating the effects of conditional execution and sparse matrices with new types of vector instruction. The fourth technique increases the peak performance of a vector machine by adding more parallel execution units in the form of additional *lanes*. The fifth technique reduces start-up overhead by pipelining and overlapping instruction start-up.

# Chaining—the Concept of Forwarding Extended to Vector Registers

Consider the simple vector sequence

MULV.D V1,V2,V3 ADDV.D V4,V1,V5 In VMIPS, as it currently stands, these two instructions must be put into two separate convoys, since the instructions are dependent. On the other hand, if the vector register, V1 in this case, is treated not as a single entity but as a group of individual registers, then the ideas of forwarding can be conceptually extended to work on individual elements of a vector. This insight, which will allow the ADDV.D to start earlier in this example, is called *chaining*. Chaining allows a vector operation to start as soon as the individual elements of its vector source operand become available: The results from the first functional unit in the chain are "forwarded" to the second functional unit. In practice, chaining is often implemented by allowing the processor to read and write a particular register at the same time, albeit to different elements. Early implementations of chaining worked like forwarding, but this restricted the timing of the source and destination instructions in the chain. Recent implementations use *flexible chaining*, which allows a vector instruction to chain to essentially any other active vector instruction, assuming that no structural hazard is generated. Flexible chaining requires simultaneous access to the same vector register by different vector instructions, which can be implemented either by adding more read and write ports or by organizing the vector-register file storage into interleaved banks in a similar way to the memory system. We assume this type of chaining throughout the rest of this appendix.

Even though a pair of operations depend on one another, chaining allows the operations to proceed in parallel on separate elements of the vector. This permits the operations to be scheduled in the same convoy and reduces the number of chimes required. For the previous sequence, a sustained rate (ignoring start-up) of two floating-point operations per clock cycle, or one chime, can be achieved, even though the operations are dependent! The total running time for the above sequence becomes

Vector length + Start-up time<sub>ADDV</sub> + Start-up time<sub>MULV</sub>

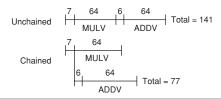

Figure F.10 shows the timing of a chained and an unchained version of the above pair of vector instructions with a vector length of 64. This convoy requires one chime; however, because it uses chaining, the start-up overhead will be seen in the actual timing of the convoy. In Figure F.10, the total time for chained operation is 77 clock cycles, or 1.2 cycles per result. With 128 floating-point operations

**Figure F.10** Timings for a sequence of dependent vector operations ADDV and MULV, both unchained and chained. The 6- and 7-clock-cycle delays are the latency of the adder and multiplier.

done in that time, 1.7 FLOPS per clock cycle are obtained. For the unchained version, there are 141 clock cycles, or 0.9 FLOPS per clock cycle.

Although chaining allows us to reduce the chime component of the execution time by putting two dependent instructions in the same convoy, it does not eliminate the start-up overhead. If we want an accurate running time estimate, we must count the start-up time both within and across convoys. With chaining, the number of chimes for a sequence is determined by the number of different vector functional units available in the processor and the number required by the application. In particular, no convoy can contain a structural hazard. This means, for example, that a sequence containing two vector memory instructions must take at least two convoys, and hence two chimes, on a processor like VMIPS with only one vector load-store unit.

We will see in Section F.6 that chaining plays a major role in boosting vector performance. In fact, chaining is so important that every modern vector processor supports flexible chaining.

## **Conditionally Executed Statements**

From Amdahl's Law, we know that the speedup on programs with low to moderate levels of vectorization will be very limited. Two reasons why higher levels of vectorization are not achieved are the presence of conditionals (if statements) inside loops and the use of sparse matrices. Programs that contain if statements in loops cannot be run in vector mode using the techniques we have discussed so far because the if statements introduce control dependences into a loop. Likewise, sparse matrices cannot be efficiently implemented using any of the capabilities we have seen so far. We discuss strategies for dealing with conditional execution here, leaving the discussion of sparse matrices to the following subsection.

Consider the following loop:

This loop cannot normally be vectorized because of the conditional execution of the body; however, if the inner loop could be run for the iterations for which  $A(i) \neq 0$ , then the subtraction could be vectorized. In Appendix G, we saw that conditionally executed instructions are a type of instruction, not a subset of normal instructions. Conditionally executed instructions could turn such control dependences into data dependences, enhancing the ability to parallelize the loop. Vector processors can benefit from an equivalent capability for vectors.

The extension that is commonly used for this capability is *vector-mask* control. The vector-mask control uses a Boolean vector of length MVL to control the execution of a vector instruction just as conditionally executed instructions use a Boolean condition to determine whether an instruction is executed. When

the vector-mask register is enabled, any vector instructions executed operate only on the vector elements whose corresponding entries in the vector-mask register are 1. The entries in the destination vector register that correspond to a 0 in the mask register are unaffected by the vector operation. If the vector-mask register is set by the result of a condition, only elements satisfying the condition will be affected. Clearing the vector-mask register sets it to all 1s, making subsequent vector instructions operate on all vector elements. The following code can now be used for the previous loop, assuming that the starting addresses of A and B are in Ra and Rb, respectively:

```

L۷

V1,Ra

;load vector A into V1

L۷

V2,Rb

:load vector B

L.D

F0,#0

;load FP zero into FO

SNEVS.D

V1,F0

;sets VM(i) to 1 if V1(i)!=F0

SUBV.D

V1, V1, V2

;subtract under vector mask

CVM

;set the vector mask to all 1s

SV

Ra, V1

;store the result in A

```

Most recent vector processors provide vector-mask control. The vector-mask capability described here is available on some processors, but others allow the use of the vector mask with only a subset of the vector instructions.

Using a vector-mask register does, however, have disadvantages. When we examined conditionally executed instructions, we saw that such instructions still require execution time when the condition is not satisfied. Nonetheless, the elimination of a branch and the associated control dependences can make a conditional instruction faster even if it sometimes does useless work. Similarly, vector instructions executed with a vector mask still take execution time, even for the elements where the mask is 0. Likewise, even with a significant number of 0s in the mask, using vector-mask control may still be significantly faster than using scalar mode. In fact, the large difference in potential performance between vector and scalar mode makes the inclusion of vector-mask instructions critical.

Second, in some vector processors the vector mask serves only to disable the storing of the result into the destination register, and the actual operation still occurs. Thus, if the operation in the previous example were a divide rather than a subtract and the test was on B rather than A, false floating-point exceptions might result since a division by 0 would occur. Processors that mask the operation as well as the storing of the result avoid this problem.

## Sparse Matrices

There are techniques for allowing programs with sparse matrices to execute in vector mode. In a sparse matrix, the elements of a vector are usually stored in some compacted form and then accessed indirectly. Assuming a simplified sparse structure, we might see code that looks like this:

do 100 i = 1,n

$$A(K(i)) = A(K(i)) + C(M(i))$$

This code implements a sparse vector sum on the arrays A and C, using index vectors K and M to designate the nonzero elements of A and C. (A and C must have the same number of nonzero elements—n of them.) Another common representation for sparse matrices uses a bit vector to say which elements exist and a dense vector for the nonzero elements. Often both representations exist in the same program. Sparse matrices are found in many codes, and there are many ways to implement them, depending on the data structure used in the program.