## **Computer Architecture**

# The Language of the Machine

## **Instruction Sets**

- ° Basic ISA

- ° Classes, Addressing, Format

- Administrative Matters

- ° Operations, Branching, Calling conventions

- ° Break

### **Organization**

- ° All computers consist of five components

- Processor: (1) datapath and (2) control

- (3) **Memory**

- (4) Input devices and (5) Output devices

- ° Not all "memory" are created equally

- Cache: fast (expensive) memory are placed closer to the processor

- Main memory: less expensive memory--we can have more

- Input and output (I/O) devices have the messiest organization

- Wide range of speed: graphics vs. keyboard

- Wide range of requirements: speed, standard, cost ...

- Least amount of research (so far)

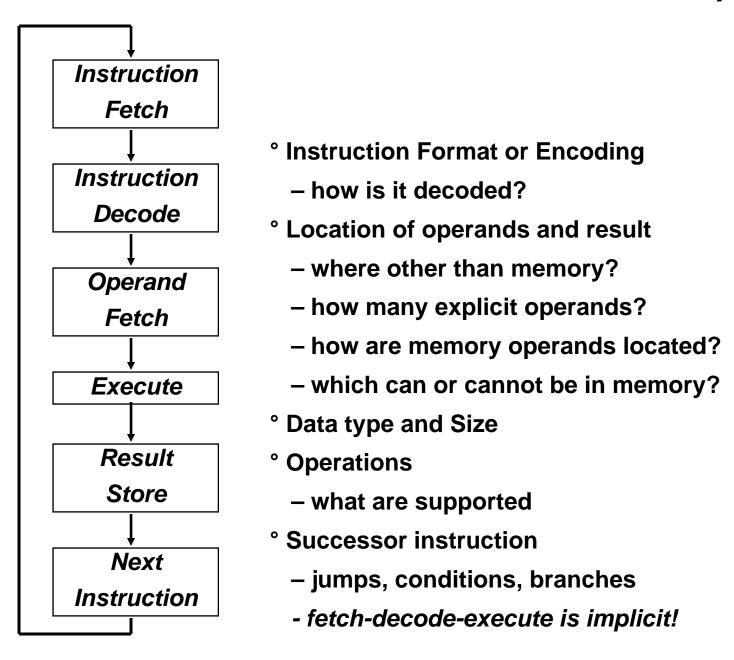

### Instruction Set Architecture: What Must be Specified?

## **RISC** features

- Reduced Instruction Set

- General Purpose Register File (large number: 32 or more)

- ° Load/Store Architecture

- ° Few Addressing modes

- Fixed Instruction Format

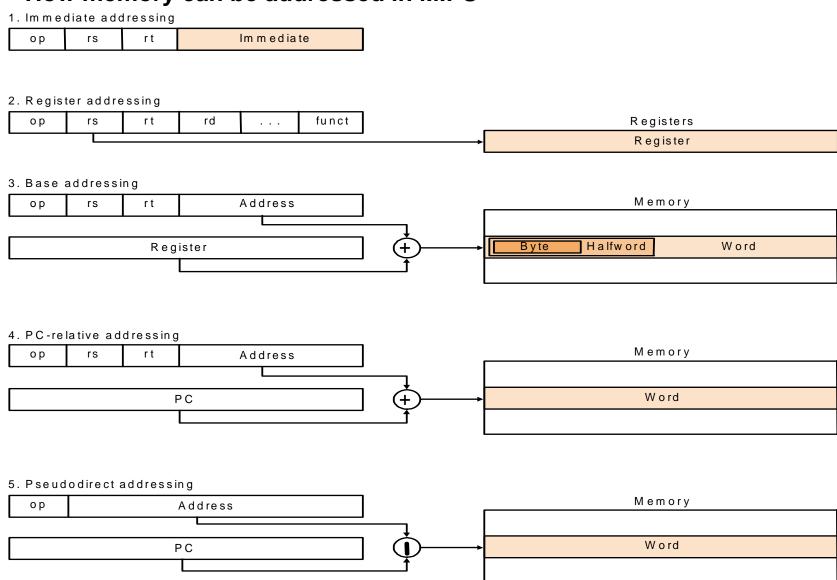

#### MIPS Addressing Formats (Summary)

#### How memory can be addressed in MIPS

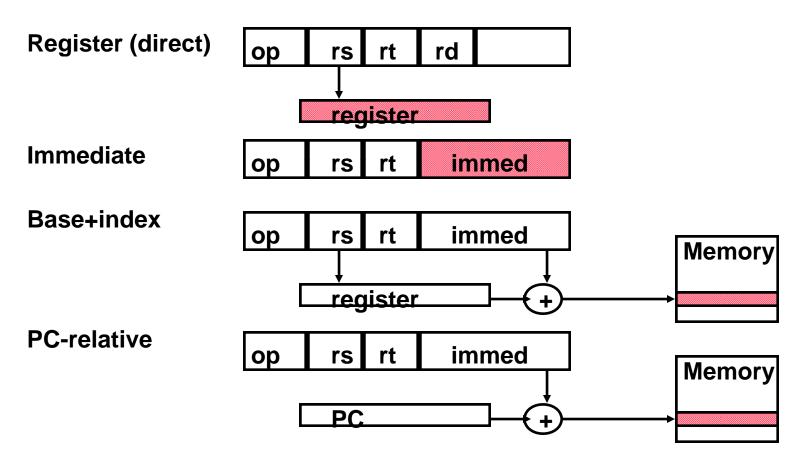

## **MIPS Addressing Modes/Instruction Formats**

#### All instructions 32 bits wide

Register Indirect?

## **MIPS I Operation Overview**

- ° Arithmetic logical

- ° Add, AddU, Sub, SubU, And, Or, Xor, Nor, SLT, SLTU

- ° Addl, AddlU, SLTI, SLTIU, Andl, Orl, Xorl, LUI

- ° SLL, SRL, SRA, SLLV, SRLV, SRAV

- Memory Access

- ° LB, LBU, LH, LHU, LW, LWL,LWR

- ° SB, SH, SW, SWL, SWR

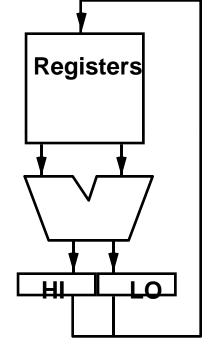

## **Multiply / Divide**

- ° Start multiply, divide

- MULT rs, rt

- MULTU rs, rt

- DIV rs, rt

- DIVU rs, rt

- Move result from multiply, divide

- MFHI rd

- MFLO rd

- ° Move to HI or LO

- MTHI rd

- MTLO rd

Why not Third field for destination? (Hint: how many clock cycles for multiply or divide vs. add?)

## **Data Types**

Bit: 0, 1

Bit String: sequence of bits of a particular length

4 bits is a nibble

8 bits is a byte

16 bits is a half-word

32 bits is a word

64 bits is a double-word

#### **Character:**

ASCII 7 bit code

#### **Decimal:**

digits 0-9 encoded as 0000b thru 1001b two decimal digits packed per 8 bit byte

#### **Integers**:

2's Complement

#### **Floating Point:**

Single Precision

Double Precision

Extended Precision

mantissa

exponent

base

How many +/- #'s?

Where is decimal pt?

How are +/- exponents

represented?

#### **MIPS** arithmetic instructions

| Instruction       | Example           | Meaning               | Comments                         |

|-------------------|-------------------|-----------------------|----------------------------------|

| add               | add \$1,\$2,\$3   | 1 = 2 + 3             | 3 operands; exception possible   |

| subtract          | sub \$1,\$2,\$3   | 1 = 2 - 3             | 3 operands; exception possible   |

| add immediate     | addi \$1,\$2,100  | 1 = 2 + 100           | + constant; exception possible   |

| add unsigned      | addu \$1,\$2,\$3  | 1 = 2 + 3             | 3 operands; no exceptions        |

| subtract unsigned | subu \$1,\$2,\$3  | 1 = 2 - 3             | 3 operands; <u>no exceptions</u> |

| add imm. unsign.  | addiu \$1,\$2,100 | 1 = 2 + 100           | + constant; no exceptions        |

| multiply          | mult \$2,\$3      | Hi, Lo = $2 \times 3$ | 64-bit signed product            |

| multiply unsigned | multu\$2,\$3      | Hi, Lo = $2 \times 3$ | 64-bit unsigned product          |

| divide            | div \$2,\$3       | $Lo = \$2 \div \$3,$  | Lo = quotient, Hi = remainder    |

|                   |                   | $Hi = $2 \mod $3$     |                                  |

| divide unsigned   | divu \$2,\$3      | $Lo = \$2 \div \$3,$  | Unsigned quotient & remainder    |

|                   |                   | $Hi = $2 \mod $3$     |                                  |

| Move from Hi      | mfhi \$1          | \$1 = Hi              | Used to get copy of Hi           |

| Move from Lo      | mflo \$1          | \$1 = Lo              | Used to get copy of Lo           |

Which add for address arithmetic? Which add for integers?

## **MIPS logical instructions**

| Instruction         | Example           | Meaning                | Comment                        |

|---------------------|-------------------|------------------------|--------------------------------|

| and                 | and \$1,\$2,\$3   | \$1 = \$2 & \$3        | 3 reg. operands; Logical AND   |

| or                  | or \$1,\$2,\$3    | \$1 = \$2   \$3        | 3 reg. operands; Logical OR    |

| xor                 | xor \$1,\$2,\$3   | <b>\$1 = \$2 ⊕ \$3</b> | 3 reg. operands; Logical XOR   |

| nor                 | nor \$1,\$2,\$3   | \$1 = ~(\$2  \$3)      | 3 reg. operands; Logical NOR   |

| and immediate       | andi \$1,\$2,10   | \$1 = \$2 & 10         | Logical AND reg, constant      |

| or immediate        | ori \$1,\$2,10    | \$1 = \$2   10         | Logical OR reg, constant       |

| xor immediate       | xori \$1, \$2,10  | \$1 = ~\$2 &~10        | Logical XOR reg, constant      |

| shift left logical  | sll \$1,\$2,10    | \$1 = \$2 << 10        | Shift left by constant         |

| shift right logical | srl \$1,\$2,10    | \$1 = \$2 >> 10        | Shift right by constant        |

| shift right arithm. | sra \$1,\$2,10    | \$1 = \$2 >> 10        | Shift right (sign extend)      |

| shift left logical  | sllv \$1,\$2,\$3  | \$1 = \$2 << \$3       | Shift left by variable         |

| shift right logical | srlv \$1,\$2, \$3 | \$1 = \$2 >> \$3       | Shift right by variable        |

| shift right arithm. | srav \$1,\$2, \$3 | \$1 = \$2 >> \$3       | Shift right arith. by variable |

#### **MIPS** data transfer instructions

| Instruction    | <u>Comment</u>         |

|----------------|------------------------|

| SW 500(R4), R3 | Store word             |

| SH 502(R2), R3 | Store half             |

| SB 41(R3), R2  | Store byte             |

|                |                        |

| LW R1, 30(R2)  | Load word              |

| LH R1, 40(R3)  | Load halfword          |

| LHU R1, 40(R3) | Load halfword unsigned |

| LB R1, 40(R3)  | Load byte              |

| LBU R1, 40(R3) | Load byte unsigned     |

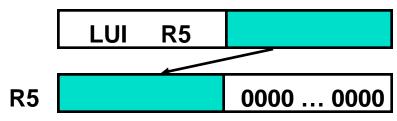

LUI R1, 40 Load Upper Immediate (16 bits shifted left by 16)

Why need LUI?

## **Methods of Testing Condition**

° Condition Codes

Processor status bits are set as a side-effect of arithmetic instructions (possibly on Moves) or explicitly by compare or test instructions.

ex: add r1, r2, r3

bz label

° Condition Register

Ex: cmp r1, r2, r3

bgt r1, label

° Compare and Branch

Ex: bgt r1, r2, label

## **MIPS Compare and Branch**

- Compare and Branch

- BEQ rs, rt, offset if R[rs] == R[rt] then PC-relative branch

- BNE rs, rt, offset <>

- Compare to zero and Branch

- BLEZ rs, offset if R[rs] <= 0 then PC-relative branch

- BGTZ rs, offset >

- BLT <

- BGEZ >=

- BLTZAL rs, offset if R[rs] < 0 then branch and link (into R 31)

- BGEZAL >=

- ° Remaining set of compare and branch take two instructions

- Almost all comparisons are against zero!

## MIPS jump, branch, compare instructions

| Instruction         | Example                              | Meaning                                                    |

|---------------------|--------------------------------------|------------------------------------------------------------|

| branch on equal     | beq \$1,\$2,100<br>Equal test; PC re | if (\$1 == \$2) go to PC+4+100 elative branch              |

| branch on not eq.   | bne \$1,\$2,100<br>Not equal test; P | if (\$1!= \$2) go to PC+4+100<br>PC relative               |

| set on less than    | slt \$1,\$2,\$3<br>Compare less th   | if (\$2 < \$3) \$1=1; else \$1=0<br>an; 2's comp.          |

| set less than imm.  | slti \$1,\$2,100<br>Compare < cons   | if (\$2 < 100) \$1=1; else \$1=0<br>etant; 2's comp.       |

| set less than uns.  |                                      | if (\$2 < \$3) \$1=1; else \$1=0<br>an; natural numbers    |

| set I. t. imm. uns. |                                      | if (\$2 < 100) \$1=1; else \$1=0<br>etant; natural numbers |

| jump                | j 10000<br>Jump to target a          | •                                                          |

| jump register       | jr \$31<br>For switch, proce         |                                                            |

| jump and link       | jal 10000<br>For procedure ca        | \$31 = PC + 4; go to 10000                                 |

### Signed vs. Unsigned Comparison

Value?

2's comp Unsigned?

```

R1= 0...00 0000 0000 0000 0001 two R2= 0...00 0000 0000 0000 0010 two R3= 1...11 1111 1111 1111 1111 two

```

#### ° After executing these instructions:

```

slt r4,r2,r1; if (r2 < r1) r4=1; else r4=0

slt r5,r3,r1; if (r3 < r1) r5=1; else r5=0

sltu r6,r2,r1; if (r2 < r1) r6=1; else r6=0

sltu r7,r3,r1; if (r3 < r1) r7=1; else r7=0</pre>

```

## ° What are values of registers r4 - r7? Why?

$$r4 = ; r5 = ; r6 = ; r7 = ;$$

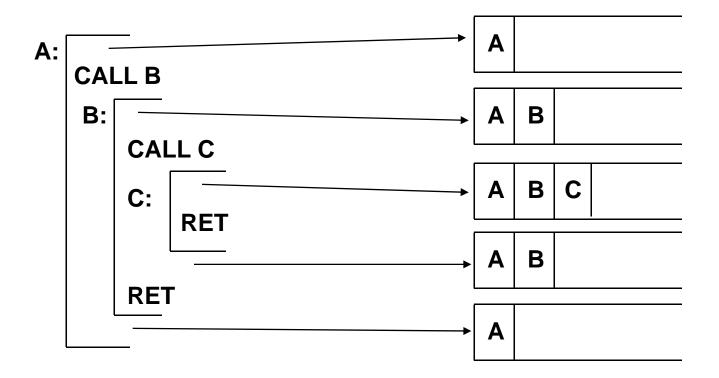

### **Calls: Why Are Stacks So Great?**

Stacking of Subroutine Calls & Returns and Environments:

Some machines provide a memory stack as part of the architecture (e.g., VAX)

Sometimes stacks are implemented via software convention (e.g., MIPS)

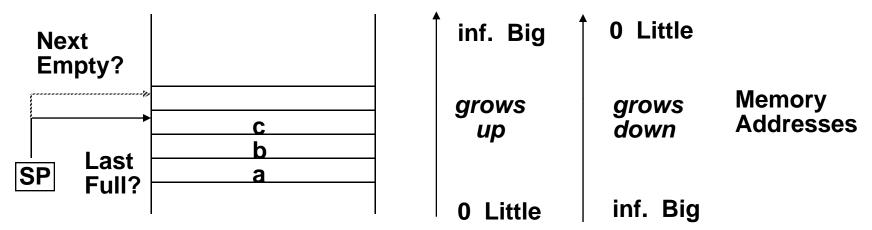

### **Memory Stacks**

Useful for stacked environments/subroutine call & return even if operand stack not part of architecture

Stacks that Grow Up vs. Stacks that Grow Down:

How is empty stack represented?

<u>Little --> Big/Last Full</u> <u>Little --> Big/Next Empty</u>

POP: Read from Mem(SP) POP: Decrement SP

**Decrement SP**

PUSH: Increment SP PUSH: Write to Mem(SP)

Write to Mem(SP) Increment SP

Read from Mem(SP)

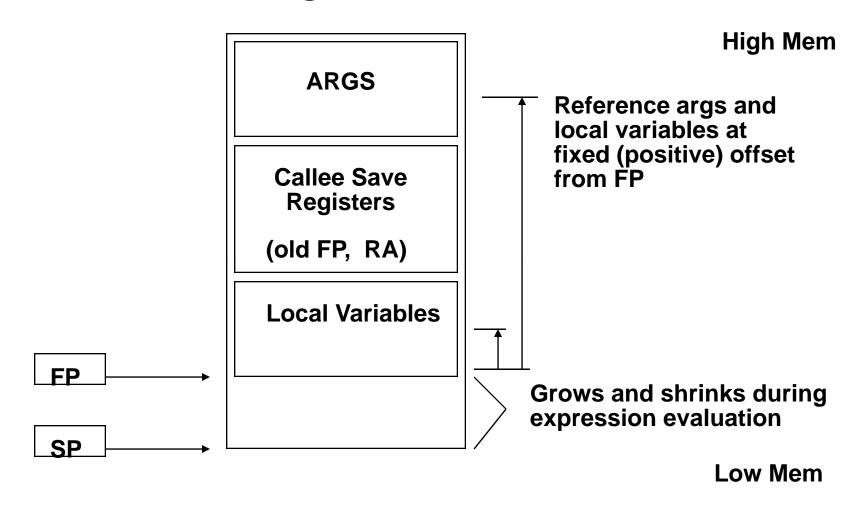

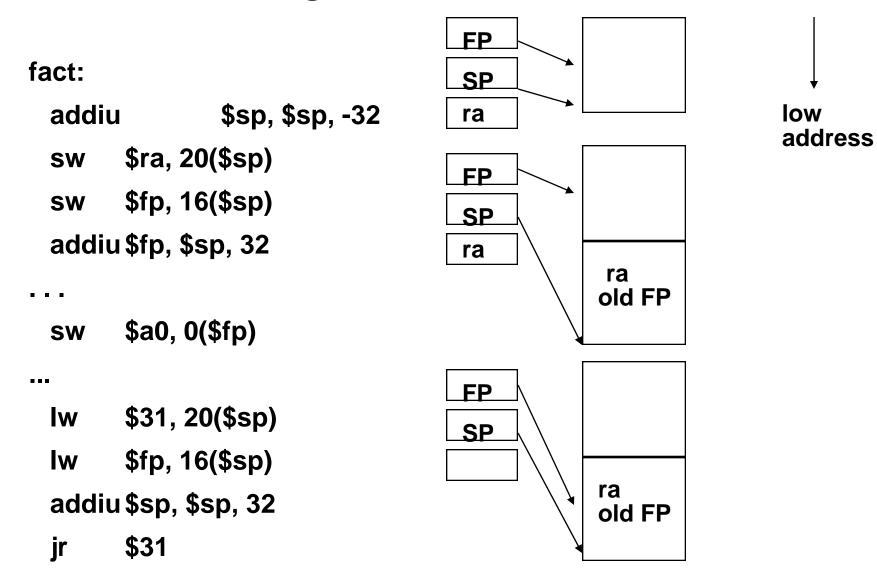

### **Call-Return Linkage: Stack Frames**

- Many variations on stacks possible (up/down, last pushed / next )

- Block structured languages contain link to lexically enclosing frame

- Compilers normally keep scalar variables in registers, not memory!

## MIPS: Software conventions for Registers

```

s0 callee saves

zero constant 0

16

reserved for assembler

... (caller can clobber)

v0 expression evaluation &

23

s7

function results

t8

temporary (cont'd)

24

a0

arguments

25

t9

k0 reserved for OS kernel

5

26

a1

a2

27

k1

6

gp Pointer to global area

a3

28

temporary: caller saves

sp Stack pointer

t0

29

fp frame pointer

(callee can clobber)

30

31

Return Address (HW)

15 t7

ra

```

Plus a 3-deep stack of mode bits.

## **MIPS / GCC Calling Conventions**

First four arguments passed in registers.

#### **Details of the MIPS instruction set**

- Register zero <u>always</u> has the value <u>zero</u> (even if you try to write it)

- Branch/jump <u>and link</u> put the return addr. PC+4 into the link register (R31)

- All instructions change <u>all 32 bits</u> of the destination register (including lui, lb, lh) and all read all 32 bits of sources (add, sub, and, or, ...)

- ° Immediate arithmetic and logical instructions are extended as follows:

- logical immediates ops are zero extended to 32 bits

- arithmetic immediates ops are sign extended to 32 bits (including addu)

- ° The data loaded by the instructions lb and lh are extended as follows:

- Ibu, Ihu are zero extended

- Ib, Ih are sign extended

- Overflow can occur in these arithmetic and logical instructions:

- add, sub, addi

- it <u>cannot</u> occur in addu, subu, addiu, and, or, xor, nor, shifts, mult, multu, div, divu

#### MIPS Instructions (Quick Summary)

| Name                               | Example                      | Comments                                                                    |  |

|------------------------------------|------------------------------|-----------------------------------------------------------------------------|--|

|                                    | \$s0-\$s7, \$t0-\$t9, \$zero | Fast locations for data. In MIPS, data must be in registers to perform      |  |

| 32 registers                       | \$a0-\$a3, \$v0-\$v1, \$gp,  | arithmetic. MIPS register \$zero always equals 0. Register \$at is          |  |

|                                    | \$fp, \$sp, \$ra, \$at       | reserved for the assembler to handle large constants.                       |  |

|                                    | Memory[0],                   | Accessed only by data transfer instructions. MIPS uses byte addresses, so   |  |

| 2 <sup>30</sup> memory Memory[4],, |                              | sequential words differ by 4. Memory holds data structures, such as arrays, |  |

| words                              | Memory[4294967292]           | and spilled registers, such as those saved on procedure calls.              |  |

|                                    |                              |                                                                             |  |

MIPS assembly language

| Category      | Instruction             | Example              | Meaning                                          | Comments                          |

|---------------|-------------------------|----------------------|--------------------------------------------------|-----------------------------------|

|               | add                     | add \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3                               | Three operands; data in registers |

| Arithmetic    | subtract                | sub \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3                               | Three operands; data in registers |

|               | add immediate           | addi \$s1, \$s2, 100 | \$s1 = \$s2 + 100                                | Used to add constants             |

|               | load word               | lw \$s1, 100(\$s2)   | \$s1 = Memory[\$s2 + 100]                        | Word from memory to register      |

|               | store word              | sw \$s1, 100(\$s2)   | Memory[\$s2 + 100] = \$s1                        | Word from register to memory      |

| Data transfer | load byte               | lb \$s1, 100(\$s2)   | \$s1 = Memory[\$s2 + 100]                        | Byte from memory to register      |

|               | store byte              | sb \$s1, 100(\$s2)   | Memory[\$s2 + 100] = \$s1                        | Byte from register to memory      |

|               | load upper immediate    | lui \$s1, 100        | \$s1 = 100 * 2 <sup>16</sup>                     | Loads constant in upper 16 bits   |

|               | branch on equal         | beq \$s1, \$s2, 25   | if (\$s1 == \$s2) go to<br>PC + 4 + 100          | Equal test; PC-relative branch    |

| Conditional   | branch on not equal     | bne \$s1, \$s2, 25   | if (\$s1 != \$s2) go to<br>PC + 4 + 100          | Not equal test; PC-relative       |

| branch        | set on less than        | slt \$s1, \$s2, \$s3 | if ( $$s2 < $s3$ ) $$s1 = 1$ ;<br>else $$s1 = 0$ | Compare less than; for beq, bne   |

|               | set less than immediate | slti \$s1, \$s2, 100 | if ( $$s2 < 100$ ) $$s1 = 1$ ;<br>else $$s1 = 0$ | Compare less than constant        |

|               | jump                    | j 2500               | go to 10000                                      | Jump to target address            |

| Uncondi-      | jump register           | jr \$ra              | go to \$ra                                       | For switch, procedure return      |

| tional jump   | jump and link           | jal 2500             | \$ra = PC + 4; go to 10000                       | For procedure call                |

## **Summary of RISC**

- ° Reduced Instruction Set

- General Purpose Register File (large number: 32 or more)

- ° Load/Store Architecture

- Few Addressing modes

- ° Fixed Instruction Format

#### **MIPS Architecture**

- ° 32 Registers

- Load/Store Architecture

- ° 5 Instruction Groups: Arithmetic, Logical, Data Transfer, Cond. Branch, Uncond. Jump

- ° Addressing modes: Register, Displacement, Immediate and PC-relative

- Fixed Instruction Format

### Registers

- General Purpose Register Set

- Any register can be used with any instruction

- ° MIPS programmers have agreed upon a set of guidelines that specify how each of the registers should be used. Programmers (and compilers) know that as long as they follow these guidelines, their code will work properly with other MIPS code.

## **Registers**

| Symbolic Name | Number          | Usage                      |

|---------------|-----------------|----------------------------|

| zero          | 0               | Zero                       |

| at            | 1               | Reserved for the Assembler |

| v0 – v1       | 2 - 3           | Result Registers           |

| a0 – a3       | 4 - 7           | Argument Registers 14      |

| t0 – t9       | 8 – 15, 24 - 25 | Temporary Registers 09     |

| s0 – s7       | 16 - 23         | Saved Registers 07         |

| k0 – k1       | 26 - 27         | Kernel Registers 01        |

| gp            | 28              | Global Data Pointer        |

| sp            | 29              | Stack Pointer              |

| fp            | 30              | Frame Pointer              |

| ra            | 31              | Return Address             |

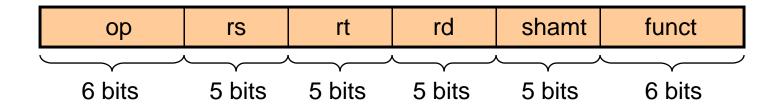

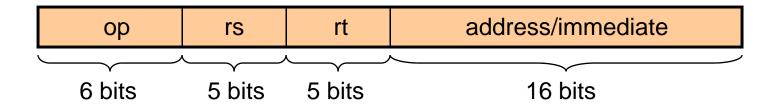

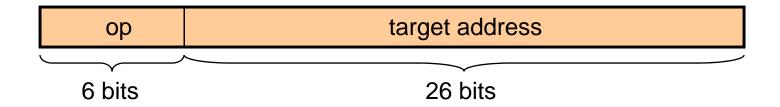

#### **Instruction Format**

Fixed Format

° 3 Format Types

• Register: R-type

• Immediate: I-type

• PC-relative: J-type

**All MIPS Instructions Format**

## R-Type

#### ° Used by

- Arithmetic Instructions

- Logic Instructions

- Except when Immediate Addressing mode used

### **I-Type**

- ° Used by

- Instructions using Immediate addressing mode

- Instructions using Displacement addressing mode

- Branch instructions

## **J-Type**

- ° Used by

- Jump Instructions

### **Instructions**

- ° 5 Groups

- Arithmetic

- Logic

- Data Transfer

- Conditional Branch

- Unconditional Jump

#### **Arithmetic**

- ° add, addu: signed and unsigned addition on registers

- ° addi, addiu: signed and unsigned addition. One operand is immediate value

- ° sub, subu: signed and unsigned subtraction on registers

- ° subi, subiu: signed and unsigned subtraction. One operand is immediate value

- ° mult, multu: signed and unsigned multiplication on registers

- ° div, divu: signed and unsigned division on registers

- ° mfc0: move from coprocessor

- ° mfhi, mflo: move from Hi and Lo registers

# Logical

- ° and, andi: logical 'AND' on registers and registers and an immediate value

- ° nor, nori: logical 'NOT OR' on registers and registers and an immediate value

- ° or, ori: logical 'OR' on registers and registers and an immediate value

- ° xor, xori: logical 'Exclusive OR' on registers and registers and an immediate value

- ° sll, sra, srl: shift left/right logical/arithmetic on registers. Size of shift can be immediate value.

- ° slt: comparison instruction: rd ← 1/0 depending on comparison outcome

#### **Data Transfer**

- ° lw, sw: load/store word

- ° lb, sb: load/store byte

- ° lbu: load byte unsigned

- ° Ih, sh: load/store halfword

- ° lui: load upper half word immediate

#### **Branch**

- ° b: branch unconditional

- o beq: branch if src1 == src2

- ° bne: branch if src1 =/= src2

- ° bgez: branch is src1 >= 0

- ° bgtz: branch if src1 > 0

- ° blez: branch if src1 <= 0

- ° bltz: branch if src1 < 0

## Jump

- ° j: jump

- ° jr: jump to src1 (address in reg src1)

- ° jal: jump and link; ra ← PC+4; jump to label

- ° jalr: jump and link; ra ← PC+4; jump to src1 (address in reg src1)

### **Addressing Modes**

- Register: all operands are registers

- Immediate: one operand is an immediate value contained in the immediate field of I-type format

- Displacement: The address of the operand is src1 + displacement. Also contained in the immediate field of I-type format

- ° PC-relative: The +/- displacement is sign extended and added to the PC

- Direct Address: used by jump instructions. The full address is provided.