# The Guide to Being a Logisim User

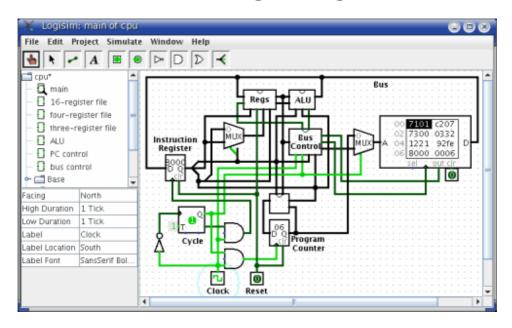

Logisim is an educational tool for designing and simulating digital logic circuits. With its simple toolbar interface and simulation of circuits as they are built, it is simple enough to facilitate learning the most basic concepts related to logic circuits. With the capacity to build larger circuits from smaller subcircuits, and to draw bundles of wires with a single mouse drag, Logisim can be used (and is used) to design and simulate entire CPUs for educational purposes.

Students at colleges and universities around the world use Logisim for a variety of purposes, including:

- A module in general-education computer science surveys

- A unit in sophomore-level computer organization courses

- Over a full semester in upper-division computer architecture courses

The Guide to Being a Logisim User, which you are reading now, is the official reference for Logisim's features. Its first part is a sequence of sections introducing the major parts of Logisim. These sections are written so that they can be read ``cover to cover" to learn about all of the most important features of Logisim.

Beginner's tutorial

Libraries and attributes

Subcircuits

Wire bundles

Combinational analysis

The remaining sections are a motley bunch of reference materials and explanations of some of the lesser corners of Logisim.

Menu reference

Memory components

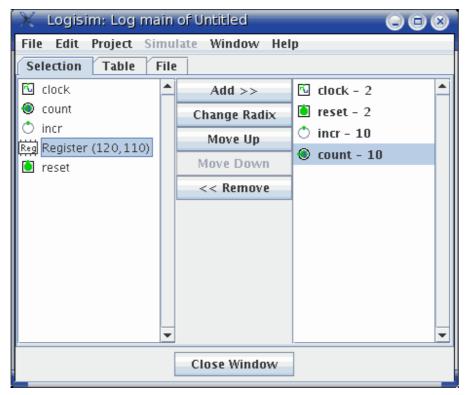

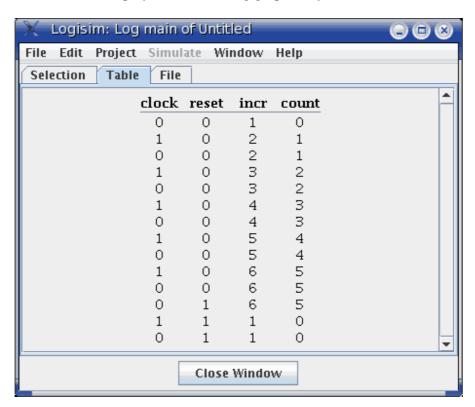

Logging

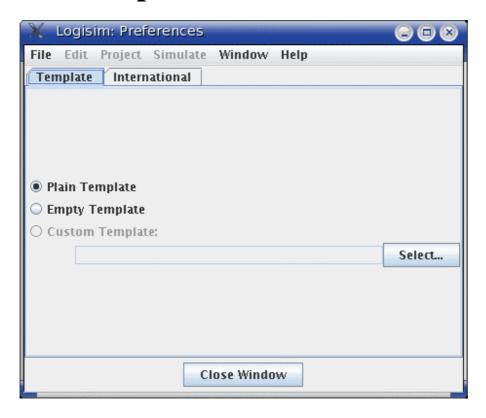

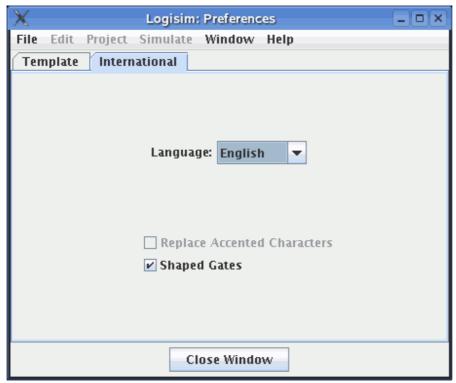

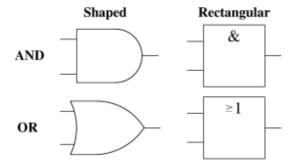

Application preferences

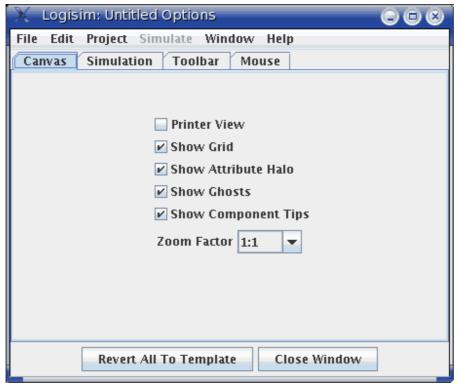

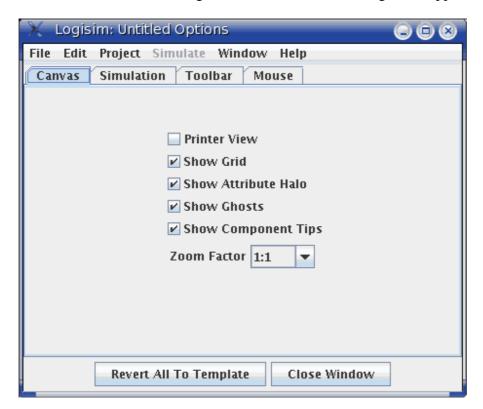

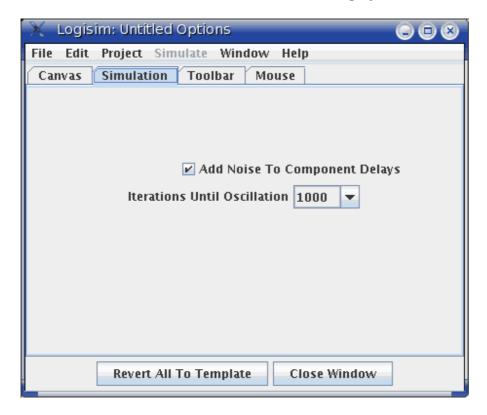

Project options

Value propagation

**JAR** libraries

About the program

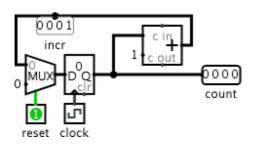

# Beginner's tutorial

Welcome to Logisim!

Logisim allows you to design and simulate digital circuits. It is intended as an educational tool, to help you learn how circuits work.

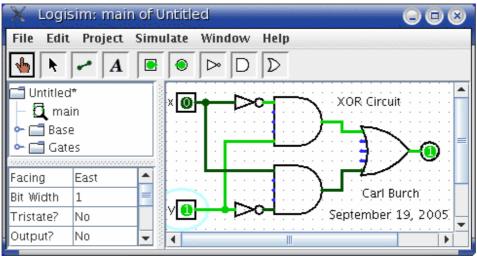

To practice using Logisim, let's build a XOR circuit - that is, a circuit that takes two inputs (which we'll call x and y) and outputs 1 if the inputs are the same and 0 if they are different. The following truth table illustrates.

| x | y | x XOR y |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

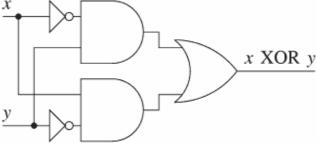

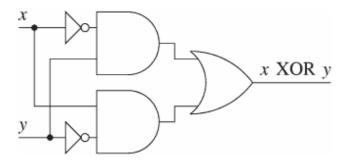

We might design such a circuit on paper.

But just because it's on paper doesn't mean it's right. To verify our work, we'll draw it in Logisim and test it. As an added bonus, we'll get a circuit that's looks nicer than what you probably would draw by hand.

Step 0: Orienting yourself Step 1: Adding gates Step 2: Adding wires

Step 3: Adding text

Step 4: Testing your circuit

Enjoy your circuit-building!

Next: Step 0: Orienting yourself

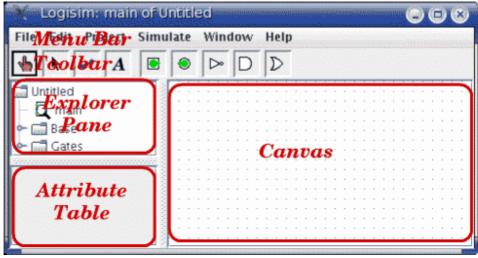

## Step 0: Orienting yourself

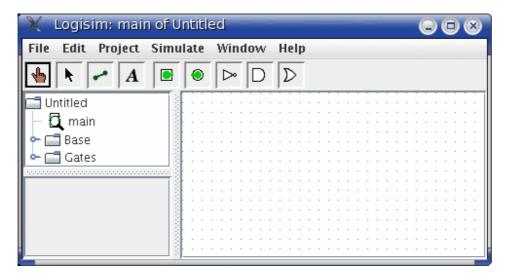

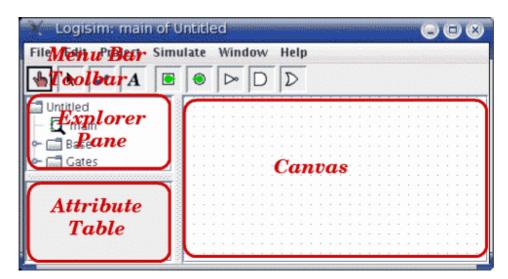

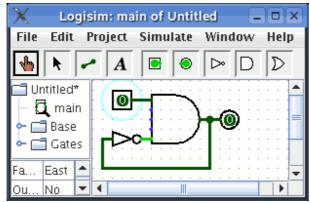

When you start Logisim, you'll see a window similar to the following. Since you'll be using a different system, some of the details may be slightly different.

All Logisim is divided into three parts, called the *explorer pane*, the *attribute table*, and the *canvas*. Above these parts are the *menu bar* and the *toolbar*.

We can quickly dispose of the explorer pane and the attribute table: We won't be examining them in this tutorial, and you can just ignore them. Also, the menu bar is self-explanatory.

That leaves the toolbar and the canvas. The canvas is where you'll draw your circuit; and the toolbar contains the tools that you'll use to accomplish this.

**Next:** Step 1: Adding gates

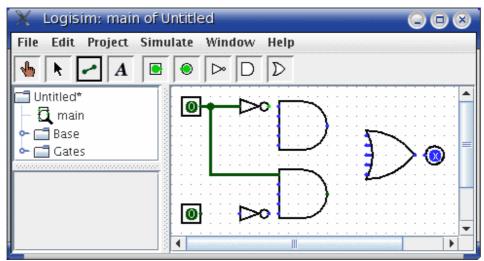

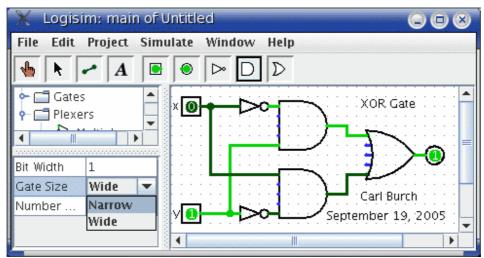

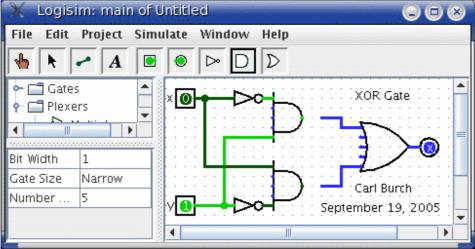

## Step 1: Adding gates

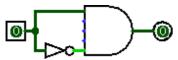

Recall that we're trying to build the following circuit in Logisim.

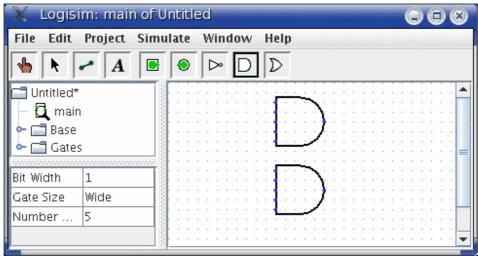

Building a circuit is easiest by inserting the gates first as a sort of skeleton for connecting wires into the circuit later. The first thing we're going to do is to add the two AND gates. Click on the AND tool in the toolbar ( $\Box$ ), the next-to-last tool listed). Then click in the editing area where you want the AND gates to go. Be sure to leave plenty of room for stuff on the left.

Notice the five dots on the left side of the AND gate. These are spots where wires can be attached. It happens that we'll just use two of them for our XOR circuit; but for other circuits, you may find that having more than two wires going to an AND gate is useful.

Now add the other gates. First click on the OR tool (D); then click where you want it. And select the NOT tool (D) and put those two gates into the canvas.

I left a little space between the NOT gates and the AND gates; if you want to, though, you can put them up against each other and save yourself the effort of drawing a wire in later.

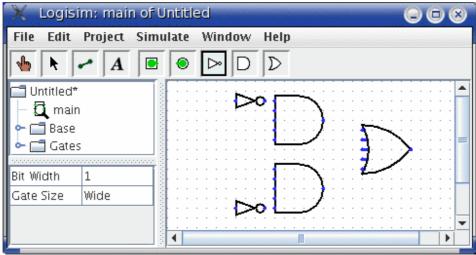

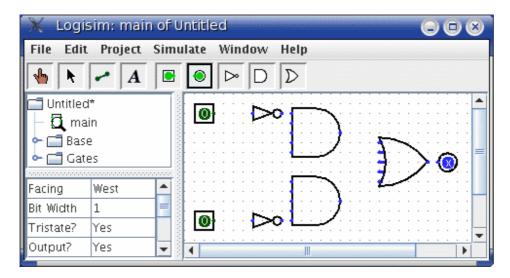

Now we want to add the two inputs x and y into the diagram. Select the input pin ( $\square$ ), and place the pins down. You should also place an output pin ( $\square$ ) next to the OR gate's output. (Again, though I'm leaving a bit of space between the OR gate and the output pin, you might choose to place them right next to each other.)

If you decide you don't like where you placed something, then you can right-click (or control-click) anything in the canvas to view a pop-up menu. Choose Delete. You can also rearrange things using the select tool ( ).

Next: Step 2: Adding wires

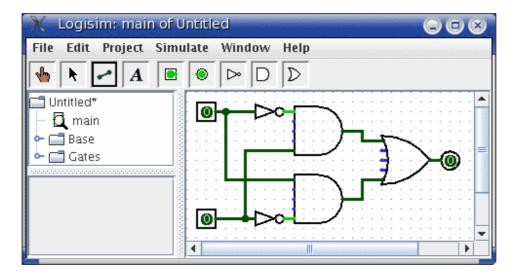

## Step 2: Adding wires

After you have all the components blocked out on the canvas, you're ready to start adding wires. Select the wiring tool (\*\*). Then start dragging from one position to another in the canvas area, and a wire will start to appear between the two points.

Wires in Logisim must be horizontal or vertical. To connect the upper input to the NOT gate and the AND gate, then, I added three different wires.

Logisim automatically connects wires to the gates and to each other. This includes automatically drawing the circle at a *T* intersection as above, indicating that the wires are connected.

As you draw wires, you may see some blue or gray wires. Blue in Logisim indicates that the value at that point is ``unknown", and gray indicates that the wire is not connected to anything. This is not a big deal temporarily. But by the time you finish your circuit, none of your wires should be blue or gray. (The unconnected legs of the OR gate will still be blue: That's fine.)

If you do have a blue or a gray wire after you think everything ought to be connected, then something is going wrong. It's important that you connect wires to the right places. Logisim draws little dots on the components to indicate where wires ought to connect. As you proceed, you'll see the dots turn from blue to light or dark green.

Once you have all the wires connected, all of the wires you inserted will themselves be light or dark green.

Next: Step 3: Adding text

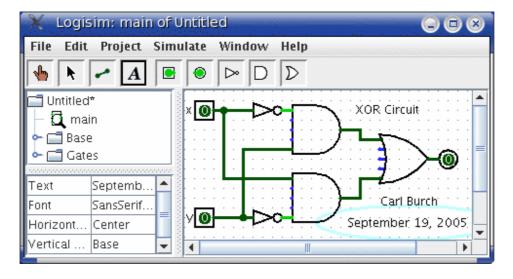

## Step 3: Adding text

Adding text to the circuit isn't necessary to make it work; but if you want to show your circuit to somebody (like a teacher), then some labels help to to communicate the purpose of the different pieces of your circuit.

Select the text tool (**A**). You can click on an input pin and start typing to give it a label. (It's better to click directly on the input pin than to click where you want the text to go, because then the label will move with the pin.) You can do the same for the output pin. Or you could just click any old place and start typing to put a label anywhere else.

Next: Step 4: Testing your circuit

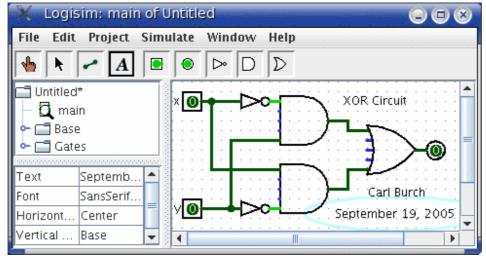

## Step 4: Testing your circuit

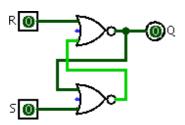

Our final step is to test our circuit to ensure that it really does what we intended. Logisim is already simulating the circuit. Let's look again at where we were.

Note that the input pins both contain 0s; and so does the output pin. This already tells us that the circuit already computes a 0 when both inputs are 0.

Now to try another combination of inputs. Select the poke tool ( and start poking the inputs by clicking on them. Each time you poke an input, its value will toggle. For example, we might first poke the bottom input.

When you change the input value, Logisim will show you what values travel down the wires by drawing them light green to indicate a 1 value or dark green (almost black) to indicate a 0 value. You can also see that the output value has changed to 1.

So far, we have tested the first two rows of our truth table, and the outputs (0 and 1) match the desired outputs.

| х | y | x XOR y |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

By poking the switches through different combinations, we can verify the other two rows. If they all match, then we're done: The circuit works!

To archive your completed work, you might want to save or print your circuit. The File menu allows this, and of course it also allows you to exit Logisim. But why quit now?

Now that you are finished with tutorial, you can experiment with Logisim by building your own circuits. If you want to build circuits with more sophisticated features, then you should navigate through the rest of the help system to see what else you can do. Logisim is a powerful program, allowing you to build up and test huge circuits; this step-by-step process just scratches the surface.

# **Libraries and Attributes**

In this section, we'll examine how to use the other two major regions of the Logisim window, the *explorer pane* and the *attribute table*.

The explorer pane

The attribute table

Tool and component attributes

**Next:** The explorer pane.

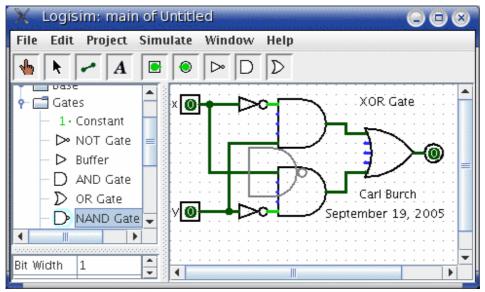

# The explorer pane

**Libraries** contain components that can be dropped into circuits. They are displayed as folders in the explorer pane; to access a library's components, you have only to double-click the corresponding folder. Below, I have opened the Gates library and selected the NAND tool from it. You can see that Logisim now stands ready to add NAND gates into the circuit.

If you look through the choices in the Gates library, you'll notice that there was no need for us to develop a XOR circuit earlier: It's built into Logisim.

When you create a project, it automatically includes the Base and Gates libraries. But Logisim includes many other libraries, too: To load one, go to the Project menu, in the Load Library submenu, and choose Built-in Library.... A dialog box will appear allowing you to choose which libraries you want to add. If you choose Plexers, for example, then you will be able to add multiplexers, demultiplexers, and decoders. You can load as many libraries as you like.

In the Load Library submenu, you can see that Logisim has three categories of libraries.

- **Built-in libraries** are libraries that are distributed with Logisim. These are documented in the *Library Reference*.

- **Logisim libraries** are projects built within Logisim and saved to the disk. You can develop a set of circuits in a single project (as described in the <u>Subcircuits</u> section of this guide) and then use that set of circuits as a library for another projects.

- **JAR libraries** are libraries that are developed in Java but not distributed with Logisim. You can download JAR libraries that others have written, or you can write your own as described in the <u>JAR Libraries</u> section of this guide. Developing a JAR library is much more difficult than developing a Logisim

library, but the components can be much fancier, including things like attributes and interaction with the user. The built-in libraries (other than Base) were written using the same API as JAR libraries can use, so they aptly demonstrate the range of functionality that the JAR libraries can support.

When loading a JAR library, Logisim will prompt you to select the JAR file, and then it will prompt you to type a class name. This class name should be provided by whoever distributed the JAR file to you.

To remove a library, choose Unload Library... from the Project menu. Logisim will prevent you from unloading libraries that contain components used in a circuit, that appear in the toolbar, or that are mapped to a mouse button.

Incidentally, a library technically contains tools, not components. Thus, in the Base library you'll find the Poke Tool ( ), the Select Tool ( ), and other tools that don't correspond directly to individual components. Most libraries, though, contain only tools for adding individual components; all built-in libraries other than the Base library are like this.

**Next:** The attribute table.

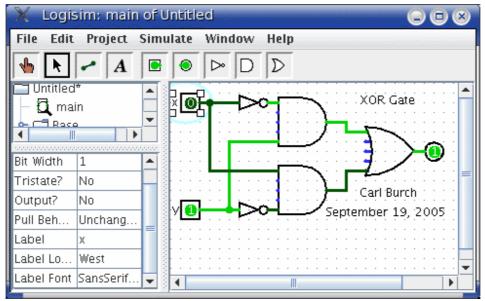

# The attribute table

Many components have **attributes**, which are properties for configuring how the component behaves or appears. The **attribute table** is for viewing and displaying a component's attribute values.

The below screen shot demonstrates what things look like after selecting the upper input of our XOR circuit and scrolling down to view the Label Font attribute.

Note the pale teal (i.e., light blue) oval surrounding the pin, called a **halo**: This indicates whose attributes are displayed in the attribute table.

To modify an attribute value, click on the value. The interface for modifying the attribute will depend on which attribute you are changing; in the case of the Label Font attribute, a dialog box will appear for selecting the new font; but some attributes (like Label) will allow you to edit the value as a text field, while others (like Label Location) will display a drop-down menu from which to select the value.

Each component type has a different set of attributes; to learn what they mean, go to the relevant documentation in the Library Reference.

Some components have attribute values that cannot be changed. One example of this is the AND gate's Gate Size attribute: As soon as you create an AND gate, is size is fixed. If you want an AND gate of a different size, then you'll need to change the attributes for the tool, which we'll discuss next.

**Next:** <u>Tool attributes</u>.

# **Tool attributes**

Every tool for adding components to a circuit also has a set of attributes, which are imparted to the components created by the tool, although the components' attributes may be changed later without affecting the tool's attributes. When you select a tool, Logisim will change the attribute table to display that tool's attributes.

For example, suppose we want to create smaller AND gates. We've already seen that an AND gate's Gate Size attribute is not editable. But the Gate Size attribute is editable for

the AND gate *tool*: To view and edit this attribute, click the tool's icon in the toolbar (or the explorer pane), and change its Gate Size attribute.

Now, we can delete the two existing AND gates and add two new AND gates in their place. This time, they will be narrow. (If you chose to reduce the number of inputs to 3, the AND gate would not have vertical extension on the left side. But you'd also have to rewire the circuit so that the wires hit the AND gate's left side.)

With some tools, the icon reflects some of the attributes' values. One example of this is with the Pin tool, whose icon faces the same way as its Facing attribute says.

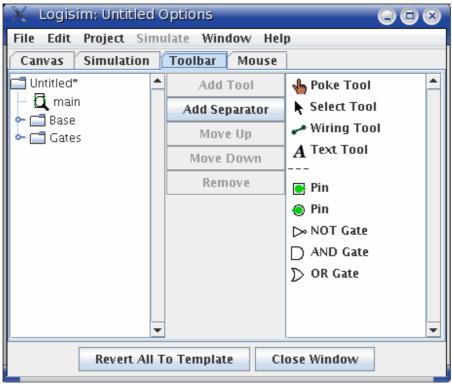

The tools in the toolbar each have a separate attribute set from the corresponding tools in the explorer pane. Thus, even though we changed the toolbar's AND tool to create narrow AND gates, the AND tool in the Gates library will still create wide AND gates unless you change its attributes too.

In fact, the input pin and output pin tools in the default toolbar are both instances of the Base library's Pin tool, but the three attribute sets are different. The icon for the Pin tool is drawn as a circle or a square depending on the value of its ``Output?" attribute.

Logisim provides a handy shortcut for changing the Facing attribute that controls the direction in which many components face: Typing an arrow key while that tool is selected automatically changes the direction of the component.

# **Subcircuits**

As you build circuits that are more and more sophisticated, you will want to build smaller circuits that you can use multiple times in larger circuits. In Logisim, such a smaller circuit that is used in a larger circuit is called a **subcircuit**.

If you're familiar with computer programming, you're familiar with the subprogram concept (called *subroutines*, *functions*, or *methods* in different languages). The subcircuit concept is analogous to the concept in computer programming, and it is used for the same purposes: To break a large job into bite-sized pieces, to save the effort of defining the same concept multiple times, and to facilitate debugging.

Creating circuits

Using subcircuits

Debugging subcircuits

Logisim libraries

**Next:** Creating circuits.

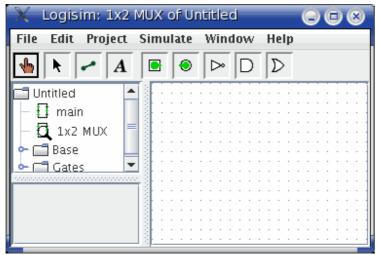

# **Creating circuits**

Every Logisim project is actually a library of circuits. In its simplest form, each project has only one circuit (called "main" by default), but it is easy to add more: Select Add Circuit... from the Project menu, and type any name you like for the new circuit you want to create.

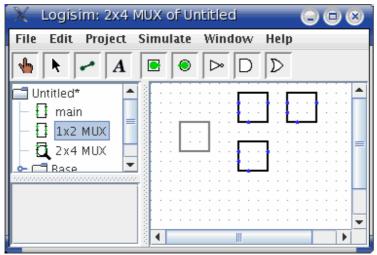

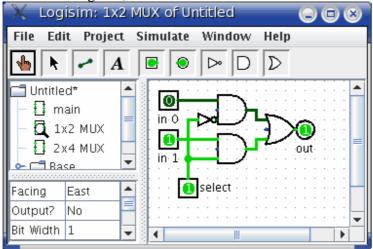

Suppose we want to build a 1x2 multiplexer named "1x2 MUX." After adding the circuit, Logisim will look like this.

In the explorer pane, you can now see that the project now contains two circuits, "main", and "1x2 MUX." Logisim draws a magnifying glass over the icon of the circuit currently being viewed; the current circuit name also appears in the window's title bar.

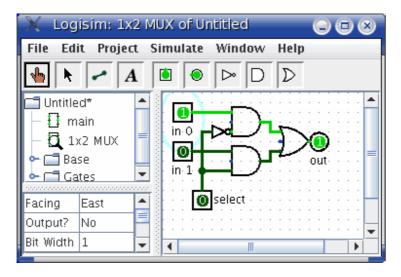

After editing the circuit to appear like a 1x2 multiplexer, we might end up with the following circuit.

Next: <u>Using subcircuits</u>.

# Using subcircuits

Now suppose we want to build a 2x4 multiplexer using instances of our 1x2 multiplexer. Of course, we would first create a new circuit, which we'll call "2x4 MUX." To add 1x2 multiplexers into our circuit, we click the 1x2 MUX circuit *once* in the explorer pane to select it as a tool, and then we can add copies of it, represented as boxes, by clicking within the canvas.

If you click the 1x2 MUX circuit *twice* in the explorer pane, then the window would switch to editing the 1x2 MUX circuit instead.

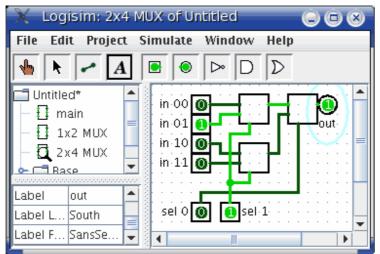

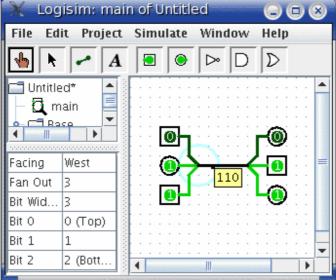

After building up the circuit, we end up with the following.

Our circuit for a 2x4 multiplexer uses three copies of the 1x2 multiplexer, each drawn as a box with pins along the side. The pins on this box correspond to the input and output pins in the 1x2 MUX circuit. The two pins on the west side of the box correspond to the two pins that face east in the 1x2 MUX circuit; the pin on the box's east side corresponds to the 1x2 MUX's west-facing pin (which happens to be an output pin); and the pin on the box's south side corresponds to the 1x2 MUX's north-facing pin. The order of the two pins on the box's west side correspond to the same top-down ordering that apears in the subcircuit. (If there were several pins on the box's north or south side, they would correspond to the same left-right order in the subcircuit.)

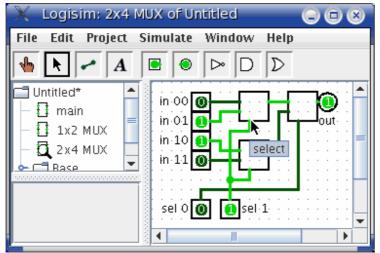

If the pins in the subcircuit's layout have labels associated with them, then Logisim will display that label in a **tip** (that is, a temporary text box) when the user hovers the mouse over the corresponding location of the subcircuit component. (If you find these tips irritating, you can disable them via the Project Options window's Canvas tab.)

Several other components will display these tips, too: For some of the pins of a built-in <u>flip-flop</u>, for example, hovering over it explains what that pin does.

Incidentally, every pin to a circuit must be either an input or an output. Many manufactured chips have pins that behave as an input in some situations and as an output in others; you cannot construct such chips within Logisim.

Logisim will maintain different state information for all subcircuits appearing in a circuit. For example, if a circuit contains a flip-flop, and that circuit is used as a subcircuit several times, then each subcircuit's flip-flop will have its own value when simulating the larger circuit.

Now that we have the 2x4 multiplexer defined, we can now use it in other circuits. Logisim has no limits on how deeply circuits can be nested - though it will object to nesting circuits within themselves!

**Note:** There's nothing wrong with editing a circuit that is being used as a subcircuit; in fact, this is quite common. Be aware, though, that any changes to a circuit's pins (adding, deleting, or moving them) will rearrange them also in the containing circuit. Thus, if you change any pins in a circuit, you will also need to edit any circuits using it as a subcircuit.

**Next:** Debugging subcircuits.

# **Debugging subcircuits**

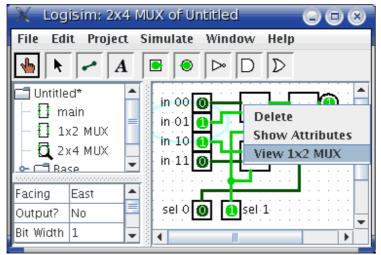

As you test larger circuits, you will likely find bugs. To nail down what's going wrong, exploring what's going on in the subcircuits while running the overall circuit can help. From viewing the overall circuit, you can do this by bringing up the subcircuit's popup menu (right-click or control-click its box). Then choose the View option.

After choosing this, the view will switch to the subcircuit.

Notice that the pins' values in the subcircuit match the values being sent to them in its containing circuit.

While in the subcircuit, you can change it however you want; any changes to pins' values will be propagated within the containing circuit. (If you attempt to toggle a pin using the Poke Tool, Logisim will pop up a dialog box asking whether you want to create a new state; responding Yes will divorce the state viewed with the subcircuit from the outer circuit's state, while responding No will cancel the toggle request.)

Once you have completed viewing and/or editing the parent circuit either by double-clicking it in the explorer pane, or via the Go Out To State submenu of the Simulate menu.

**Next:** Logisim libraries.

# **Logisim libraries**

Every Logisim project is automatically a library that can be loaded into other Logisim projects: Just save it into a file and then load the library within another project. All of the circuits defined in the first project will then be available as subcircuits for the second. This feature allows you to reuse common components across projects and to share favorite components with your friends (or students).

Each project has a designated "main circuit," which can be changed to refer to the current circuit via the Set As Main Circuit option in the Project menu. The *only* significance of this is that the main circuit is the one that is displayed when you first open the project. The default name of the circuit in a newly created file ("main") has no significance at all, and you can feel free to delete or rename that circuit.

With a loaded Logisim library, you are allowed to view circuits and manipulate their states, but Logisim will prevent you from altering them.

If you want to alter a circuit in a loaded Logisim library, then you need to open it separately within Logisim. As soon as you save it, the other project should automatically load the modified version immediately; but if it does not, you can right-click the library folder in the explorer pane and select Reload Library.

# Wire bundles

In simple Logisim circuits, most wires carry only one bit; but Logisim also allows you to create wires that bundle together multiple bits. The number of bits traveling along a wire is that wire's **bit width**.

Creating bundles

Splitters

Wire colors

Next: Creating bundles.

# **Creating bundles**

Every input and output on every component in the circuit has a bit width associated with it. Many of Logisim's built-in components include attributes allowing you to customize the bit widths of their inputs and outputs.

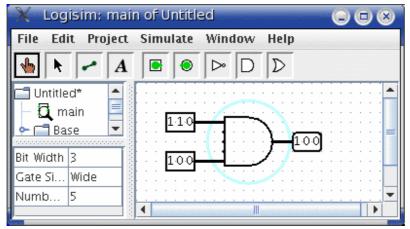

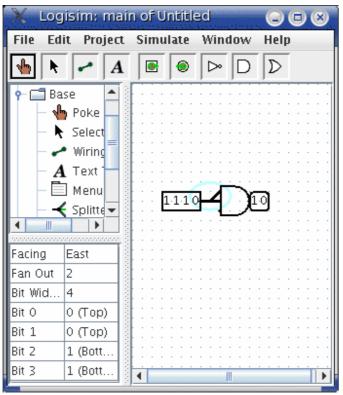

The below screen shot illustrates a simple circuit for finding the bitwise AND of two three-bit inputs; each pin has its Bit Width attribute customized for dealing with three-bit data, as with the pictured AND gate attributes.

Notice that the input and output pins are drawn with three bits, and the output is the bitwise AND of the inputs.

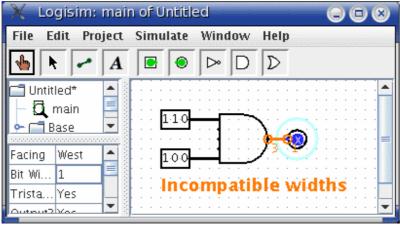

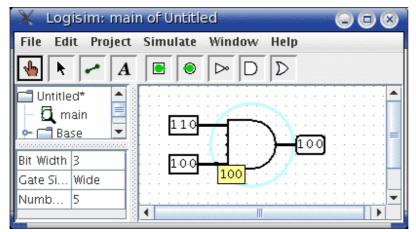

For components, all inputs and outputs must have their bit widths defined. In contrast, a wire's bit width is undefined: Instead, the wire's width adapts to the components to which it is attached. If a wire connects two components demanding different bit widths, Logisim will complain of ``Incompatible widths'' and indicate the offending locations in orange. In the below, the output pin's Bit Width attribute has been changed to 1, and so Logisim complains that the wire cannot connect a three-bit value to a one-bit value.

Wires that connect incompatible locations (drawn in orange) do not carry values.

For single-bit wires, you can see at a glance what value it is carrying because Logisim colors the wire light or dark green depending the value. It does not display values for multi-bit wires: They are simply black. You can, though, probe a wire by clicking it using the poke tool (1).

This probing feature is helpful for debugging circuits using wire bundles.

Next: Splitters.

# **Splitters**

When you work with multi-bit values, you will often want to route different bits in different directions. The Base library's splitter tool (◀ allows you to accomplish this.

For example, suppose we want to build a circuit taking an eight-bit input and outputting the AND of its two nibbles (the upper four bits and the lower four bits). We will have an eight-bit value coming from the input pin, and we want to split that into two four-bit values. In the below circuit, we have used a splitter to accomplish this.

In this example, the splitter happens to actually split an incoming value into multiple outgoing values. But splitters can also combine multiple values into a single value. In fact, they are non-directional: They can send values one way at one time and another way later, and they can even do both at the same time, as in the below example where two values are fed rightward and the middle value feeds leftward.

The key to understanding splitters is their attributes. In the following, the term *split end* refers to one of the multiple wires on one side, while the term *combined end* refers to the single wire on the other side.

- The **Facing** attribute tells where the split ends should be relative to the combined end. This cannot be changed once a splitter is dropped into the circuit.

- The **Fan Out** attribute specifies how many split ends there are. This also cannot be changed once a splitter is dropped into the circuit.

- The **Bit Width** attribute specifies the bit width of the combined end.

- The **Bit** *x* attribute says which split end corresponds to bit *x* of the combined end. If multiple bits correspond to the same split end, then their relative ordering will be the same as in the combined end. Logisim splitters cannot have a bit from the combined end correspond to multiple split ends.

Note that any change to the Fan Out or Bit Width attributes will reset all Bit *x* attributes so that they will distribute the bits of the combined value as evenly as possible among the split ends.

Next: Wire colors.

# Wire colors

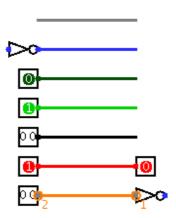

We are now in a position to summarize the full rainbow of colors that Logisim wires can take on. The following little circuit illustrates all of them at once.

- **Gray:** The wire's bit width is unknown. This occurs because the wire is not attached to any components' inputs and outputs. (All inputs and outputs have a defined bit width.)

- **Blue:** The wire is for carrying a one-bit value, but the value it is carrying is not known. In the above example, this is occurring because the NOT gate's input is unknown, and so its output is also unknown.

- **Dark green:** The wire is carrying a one-bit 0 value.

- **Bright green:** The wire is carrying a one-bit 1 value.

- **Black:** The wire is carrying a multi-bit value. Some or all of the bits may not be specified.

- **Red:** The wire is carrying an error value. This usually arises because conflicting values on the wire. (The other possibility would be that a library component is

programmed to emit an error value for another reason; in the built-in libraries, though, error values arise only from propagating other error values.) In the above example, we have one input pin placing a 0 on the wire and another placing a 1 on the wire, causing a conflict. Multi-bit wires will turn red when any of the bits carried are error values.

• **Orange:** The components attached to the wire do not agree in bit width. An orange wire is effectively "broken": It does not carry values between components.

Next: *User's Guide*.

# **Combinational analysis**

All circuits fall into one of two well-known categories: In a **combinational circuit**, all circuit outputs are a strict *combination* of the current circuit inputs, whereas in a **sequential circuit**, some outputs may depend on past inputs (the *sequence* of inputs over time).

The category of combinational circuits is the simpler of the two. Practitioners use three major techniques for summarizing the behavior of such circuits.

- logic circuits

- Boolean expressions, which allow an algebraic representation of how the circuit works

• truth tables, which list all possible input combinations and the corresponding outputs

The *Combinational Analysis* module of Logisim allows you to convert between these three representations in all directions. It is a particularly handy way of creating and understanding circuits with a handful of one-bit inputs and outputs.

**Opening Combinational Analysis**

Editing the truth table

**Creating expressions**

Generating a circuit

**Next:** Opening Combinational Analysis.

# **Opening Combinational Analysis**

The bulk of the Combinational Analysis module is accessed through a single window of that name allowing you to view truth tables and Boolean expressions. This window can be opened in two ways.

### Via the Window menu

Select Combinational Analysis, and the current Combinational Analysis window will appear. If you haven't viewed the window before, the opened window will represent no circuit at all.

Only one Combinational Analysis window exists within Logisim, no matter how many projects are open. There is no way to have two different analysis windows open at once.

## Via the Project menu

From a window for editing circuits, you can also request that Logisim analyze the current circuit by selecting the Analyze Circuit option from the Project menu. Before Logisim opens the window, it will compute Boolean expressions and a truth table corresponding to the circuit and place them there for you to view.

For the analysis to be successful, each input must be attached to an input pin, and each output must be attached to an output pin. Logisim will only analyze circuits with at most eight of each type, and all should be single-bit pins. Otherwise, you will see an error message and the window will not open.

In constructing Boolean expressions corresponding to a circuit, Logisim will first attempt to construct a Boolean expressions corresponding exactly to the gates in the circuit. But if the circuit uses some non-gate components (such as a multiplexer), or if the circuit is more than 100 levels deep (unlikely), then it will pop up a dialog box telling you that deriving Boolean expressions was impossible, and Logisim will instead derive the

expressions based on the truth table, which will be derived by quietly trying each combination of inputs and reading the resulting outputs.

After analyzing a circuit, there is no continuing relationship between the circuit and the Combinational Analysis window. That is, changes to the circuit will not be reflected in the window, nor will changes to the Boolean expressions and/or truth table in the window be reflected in the circuit. Of course, you are always free to analyze a circuit again; and, as we will see later, you can replace the circuit with a circuit corresponding to what appears in the Combinational Analysis window.

### Limitations

Logisim will not attempt to detect sequential circuits: If you tell it to analyze a sequential circuit, it will still create a truth table and corresponding Boolean expressions, although these will not accurately summarize the circuit behavior. (In fact, detecting sequential circuits is *provably impossible*, as it would amount to solving the Halting Problem. Of course, you might hope that Logisim would make at least some attempt - perhaps look for flip-flops or cycles in the wires - but it does not.) As a result, the Combinational Analysis system should not be used indiscriminately: Only use it when you are indeed sure that the circuit you are analyzing is indeed combinational!

Logisim will make a change to the original circuit that is perhaps unexpected: The Combinational Analysis system requires that each input and output have a unique name that conforming to the rules for Java identifiers. (Roughly, each character must either a letter or a digit, and the first character must be a letter. No spaces allowed!) It attempts to use the pins' existing labels, and to use a list of defaults if no label exists. If an existing label doesn't follow the Java-identifier rule, then Logisim will attempt to extract a valid name from the label if at all possible.

Incidentally, the ordering of the inputs in the truth table will match their top-down ordering in the original circuit, with ties being broken in left-right order. (The same applies to the ordering of outputs.)

**Next:** Editing the truth table.

# **Editing the truth table**

On opening the Combinational Analysis window, you will see that it consists of five tabs.

This page describes the first three tabs, Inputs, Outputs, and Table. The next page of the guide describes the last two tabs, Expression and Minimized.

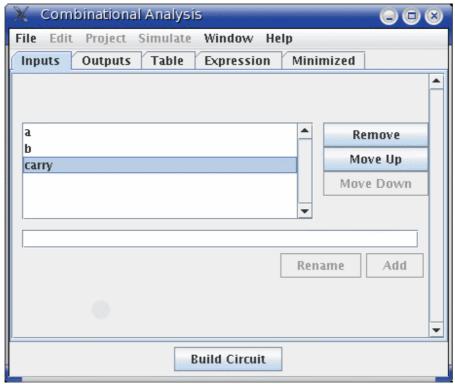

## The Inputs and Outputs tabs

The Inputs tab allows you to view and edit the list of inputs. To add new inputs, type it in the field at the pane's bottom, and click Add. If you want to rename an existing input, select it in the list in the pane's upper left region; then type the name and click Rename.

To remove an input, select it from the list and click Remove. You can also reorder the inputs (which affects the order of columns in the truth table and in the generated circuit) using the Move Up or Move Down buttons on an input.

All actions affect the truth table immediately.

The Outputs tab works in exactly the same way as the Inputs tab, except of course it works with the list of outputs instead.

#### The Table tab

The only item under the Table tab is the current truth table, diagrammed in the conventional order, with inputs constituting the columns on the left and outputs constituting the columns on the right.

You can edit the current values appearing in the output columns by clicking on the value of interest. The values will cycle through 0, 1, and x (representing a "don't care"). As we'll see on the next page, any don't-care values allow the computation of minimized expressions some flexibility.

You can also navigate and edit the truth table using the keyboard. And you can copy and paste values using the clipboard. The clipboard can be transferred to any application supporting tab-delimited text (such as a spreadsheet).

If the truth table is based on an existing circuit, you may see some pink squares in the output columns with "!!" in them. These correspond to errors that occurred while calculating the value for that row - either the circuit seemed to be oscillating, or the output value was an error value (which would be pictured as a red wire in the Logisim circuit). Hovering your mouse over the entry should bring up a tool tip describing which type of error it was. Once you click on the error entry, you will be in the 0-1-x cycle; there is no way to go back.

**Next:** Creating expressions.

# **Creating expressions**

For each output variable, the Combinational Analysis window maintains two structures - the relevant column of the truth table, and a Boolean expression - specifying how each output relates to its input. You can edit either the truth table or the expression; the other will automatically change as necessary to keep them consistent.

As we will see on the next page, the Boolean expressions are particularly useful because the Combinational Analysis window will use these when told to build a circuit corresponding to the current state.

You can view and edit the expressions using the window's last two tabs, the Expression tab and the Minimized tab.

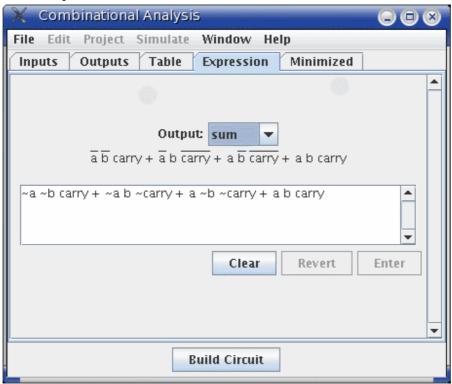

## The Expression tab

The Expression tab allows you to view and edit the current expression associated with each output variable. You can select the output expression you want to view and edit using the selector labeled "Output:" at the pane's top.

Just below the selector will appear the expression formatted in a particularly common notation, where an OR is represented as addition, an AND is represented as multiplication, and a NOT is denoted with a bar above the portion affected by the NOT.

The text pane below this displays the same information in ASCII form. Here, a NOT is represented with a tilde ('~').

You can edit the expression in the text pane and click the Enter button to make it take effect; doing this will also update the truth table to make it correspond. The Clear button clears the text pane, and the Revert button changes the pane back to representing the current expression.

Note that your edited expression will be lost if you edit the truth table.

In addition to multiplication and addition standing for AND and OR, an expression you type may contain any of C/Java logical operators, as well as simply the words themselves.

```

highest precedence \sim ! NOT (none) & && AND ^{\circ} XOR lowest precedence + | | | OR

```

The following examples are all valid representations of the same expression. You could also mix the operators.

```

~a (b + c)

!a && (b | | c)

NOT a AND (b OR c)

```

In general, parentheses within a sequence of ANDs (or ORs or XORs) do not matter. (In particular, when Logisim creates a corresponding circuit, it will ignore such parentheses.)

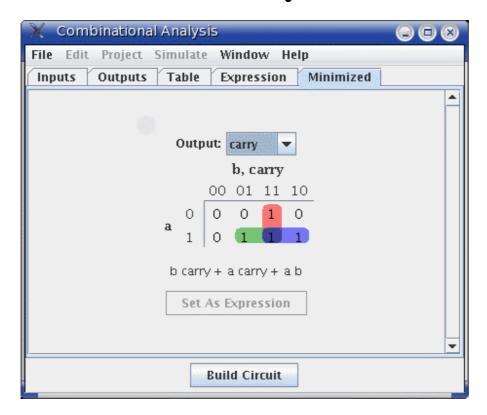

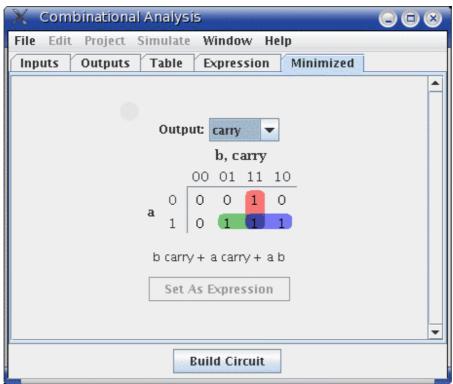

### The Minimized tab

The final tab displays a minimized sum-of-products expression corresponding to a column of the truth table. You can select which output's minimized expression you want to view using the selector at top.

If there are four or fewer inputs, a Karnaugh map corresponding to the variable will appear below the selector. You can click the Karnaugh map to change the corresponding

truth table values. The Karnaugh map will also display the currently selected terms for the minimized expression as solid semitransparent rounded rectangles.

Below this is the minimized expression itself, formatted as in the Expression tab's display. If there are more than four inputs, the Karnaugh map will not appear; but the minimized expression will still be computed. (Logisim uses the Quine-McCluskey algorithm to compute the minimized expression. This is equivalent to a Karnaugh map, but it applies to any number of input variables.)

The Set As Expression button allows you to select the minimized expression as the expression corresponding to the variable. This will generally not be necessary, as edits to the truth table result in using the minimized expression for the changed column; but if you enter an expression through the Expression tab, this can be a convenient way to switch to the corresponding minimized expression.

Next: Generating a circuit.

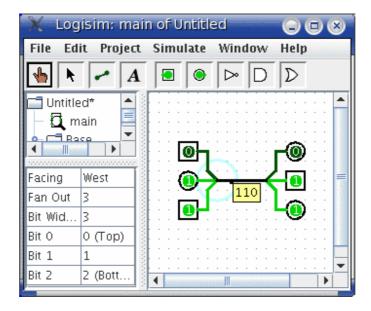

# Generating a circuit

The Build Circuit button will construct a circuit whose gates correspond to the currently chosen expressions for each output. The circuit's inputs and outputs will be displayed in top-down order corresponding to how they appear under the Inputs and Outputs tabs. Generally speaking, the constructed circuit will be attractive; and, indeed, one application of Logisim's Combinational Analysis module is to beautify poorly drawn circuits. Still, as with any automatic formatting, it will not express the structural details that a human-drawn circuit would.

When you click the Build Circuit button, a dialog box will appear prompting you to choose which project where you want the circuit and the name you wish to give it. If you type the name of an existing circuit, then that circuit will be replaced (after Logisim prompts you to confirm that you really want to do this).

The Build Circuit dialog includes two options. The Use Two-Input Gates Only option specifies that you want all gates constructed to have two inputs. (NOT gates, of course, constitute an exception to this rule.) The Use NAND Gates Only option specifies that you would like it to translate the circuit into one using only NAND gates. You can select both options if you want to use only two-input NAND gates.

Logisim cannot construct a NAND-only circuit for an expression containing any XOR operators. This option will therefore be disabled if any outputs' expressions contain XORs.

# **Menu Reference**

This section explains the six menus that accompany every major Logisim window.

The File menu

The Edit menu

The Project menu

The Simulate menu

The Window and Help menus

Many menu items relate specifically to a currently opened project. But some Logisim windows (particularly the <u>Combinational Analysis window</u> and the <u>Application Preferences window</u>) are not associated with projects. For these windows, the project-specific menu items will be disabled.

Next: The File menu.

# The File menu

#### New

Opens a new project in a new window. The project will initially be a copy of the currently selected template.

#### Open...

Opens an existing file as a project in a new window.

You can open files saved in Version 1.0X of Logisim, but there may be some slight conversion problems for complex circuits. Most notably, Logisim 1.0X computes subcircuit locations in a very different way, and you will need manually to go through all circuits and move the subcircuits to their correct locations.

#### Close

Closes all windows associated with the currently viewed project.

#### Save

Saves the currently viewed project, overwriting what was previously in the file.

### Save As...

Saves the currently viewed project, prompting the user to save into a different file than before.

#### **Export As GIF...**

Creates GIF image(s) corresponding to circuits. The configuration dialog box is described below.

### Print...

Sends circuit(s) to a printer. The configuration dialog box is described below.

#### Preferences...

Displays the <u>application preferences</u> window. (On Mac OS systems, this will appear in the Logisim menu.)

#### Exit

Closes all currently open projects and terminates Logisim. (On Mac OS systems, this will appear as Quit in the Logisim menu.)

## **Configuring Export**

When you select Export As GIF..., Logisim displays a dialog box with three options.

- **Circuits:** A list where you can select one or more circuits that should be exported into GIF files. (Empty circuits are not displayed as options.)

- **Scale Factor:** You can scale the images as they are dumped into GIF files using this slider.

- **Printer View:** Whether to use "printer view" in exporting the circuits.

After clicking OK, Logisim will display a file selection dialog box. If you have selected one circuit, select the file into which the GIF should be placed. If you have selected multiple circuits, select a directory where the files should be placed; Logisim will name the images based on the circuits' names (main.gif, for example).

## **Configuring Print**

When you choose Print..., Logisim displays a dialog box for configuring what is printed.

- **Circuits:** A list where you can select one or more circuits to be printed. (Empty circuits are not displayed as options.) Logisim will print one circuit per page. If the circuit is too large for the page, the image will be scaled down to fit.

- **Header:** Text that should appear centered at the top of each page. The following substitutions will be made into the text.

- %n Name of circuit on page

- %p Page number

- %₽ Total page count

- %% A single percent sign ('%')

- **Rotate To Fit:** If checked, then Logisim will rotate each circuit by 90 degrees when the circuit is too large to fit onto the page and it does not need to be scaled as small when rotated 90 degrees.

- **Printer View:** Whether to use ``printer view" in printing the circuits.

After clicking OK, Logisim will display the standard page setup dialog box before printing the circuits.

**Next:** The Edit menu.

# The Edit menu

### Undo XX

Undoes the most recently completed action affecting how the circuit would be saved in a file. Note that this does not include changes to the circuit state (as with manipulations performed by the Poke Tool).

#### Cut

Removes the currently selected components from the circuit onto Logisim's clipboard.

**Note:** Logisim's clipboard is maintained separately from the clipboard for the overall system; as a result, cut/copy/paste will not work across different applications, even including other running copies of Logisim. If, however, you have multiple projects open under the same Logisim process, then you should be able to cut/copy/paste between them.

### Copy

Copies the currently selected components in the circuit onto Logisim's clipboard. (See the note under the Cut menu item.)

#### **Paste**

Pastes the components on Logisim's clipboard into the current selection. (See the note under the Cut menu item.)

When you paste components, they will not immediately be dropped; instead, they will be drawn in light gray. They will not actually be `dropped" into the circuit until you either move the selection or change the selection so that the components are no longer in it.

The reason for this odd behavior is this: To be consistent with its other behavior, Logisim must immediately merge any wires as soon as they are dropped into a circuit; this merging process changes existing wires in the circuit. When you paste wires from the clipboard, however, you may to place them in a different location, and the changing inherent in the merging process would be against your wishes.

#### **Delete**

Removes all components in the current selection from the circuit.

### **Select All**

Selects all components in the current circuit.

**Next:** The Project menu.

# The Project menu

#### Add Circuit...

Adds a new circuit into the current project. Logisim will insist that you name the new circuit. The name must not match any existing circuits in the project.

#### Load Library

Loads <u>a library</u> into the project. You can load three types of libraries, as explained elsewhere in the *User's Guide*.

#### Unload Libraries...

Unloads current libraries from the circuit. Logisim will not permit you to unload any libraries currently being used, including libraries containing components appearing in any project circuits, as well as those with tools that appear in the toolbar or that are mapped to the mouse.

### **Analyze Circuit**

Computes a truth table and Boolean expressions corresponding to the current circuit, displaying them in <u>the Combinational Analysis window</u>. The analysis process will only be valid for combinational circuits. A full description of the analysis process is described <u>in the Combinational Analysis section</u>.

#### Rename Circuit...

Renames the currently displayed circuit.

#### **Set As Main Circuit**

Sets the currently displayed circuit to be the project's ``main circuit." (This menu item will be grayed out if the current circuit is already the project's main circuit.) The only significance of the main circuit is that it is the circuit that first appears when a project file is opened.

#### Remove Circuit...

Removes the currently displayed circuit from the project. Logisim will prevent you from removing circuits that are used as subcircuits, and it will prevent you from removing the final circuit in a project.

### Options...

Opens the Project Options window.

**Next:** The Simulate menu.

# The Simulate menu

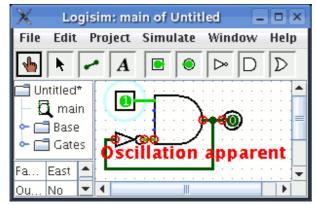

### **Simulate Enabled**

If checked, circuits viewed will be "live:" That is, the values propagating through the circuit will be updated with each poke or change to the circuit.

The menu option will be automatically unchecked if circuit oscillation is detected.

#### **Reset Simulation**

Clears everything about the current circuit's state, so that it is as if you have just opened the file again. If you are viewing a subcircuit's state, the entire hierarchy is cleared.

#### Go Out To State

When you <u>delve into a subcircuit's state</u> via its pop-up menu, this menu lists the circuits above the currently viewed circuit's state. Selecting one displays the corresponding circuit.

#### Go In To State

If you have delved into a subcircuit's state and then moved back out, this menu lists the subcircuits below the current circuit. Selecting one of the circuits displays the corresponding circuit.

#### **Tick Once**

Steps one tick forward into the simulation. This can be useful when you want to step the clocks manually, particularly when the clock is not in the same circuit that you are currently viewing.

#### **Ticks Enabled**

Starts automatically ticking the clock. This will have an effect only if the circuit contains any clock devices (in the Base library). The option is disabled by default.

### **Tick Frequency**

Allows you to select how often ticks occur. For example, 8 Hz means that ticks will occur eight times a second. A tick is the base unit of measurement for the speed of clocks.

Note that the clock cycle speed will be slower than the tick speed: The fastest possible clock will have a one-tick up cycle and a one-tick down cycle; such a clock would have up/down cycle rate of 4 Hz if the ticks occur at 8 Hz.

### Logging...

Enters the <u>logging module</u>, which facilitates automatically noting and saving values in a circuit as a simulation progresses.

**Next:** The Window and Help menus.

## The Window menu

#### Minimize

Minimizes (iconifies) the current window.

#### Zoom

Resizes the current window to its preferred size.

### **Combinational Analysis**

Shows the current <u>Combinational Analysis</u> window, without changing any of its contents.

#### individual window titles

Brings the respective window to the front.

## The Help menu

#### **Tutorial**

Opens the on-line help system to the 'Beginner's Tutorial' section of the Guide to Being a Logisim User.

#### User's Guide

Opens the on-line help system to the *Guide to Being a Logisim User*.

#### **Library Reference**

Opens the on-line help system to the *Library Reference*.

#### About...

Displays a window containing the version number, mixed among the splash screen graphics. (On Mac OS, this menu item is under the Logisim menu.)

## Library Reference

A Logisim library holds a set of *tools* that allow you to interact with a circuit via clicking and dragging the mouse in the canvas area. Most often, a tool is intended for adding components of a particular type into a circuit; but some of the most important tools, such as the Poke Tool and the Select Tool, allow you to interact with components in other

All of the tools included in Logisim's built-in libraries are documented in this reference material.

#### **Base library**

- Poke Tool

- Select Tool

- Wiring Tool

- **A** Text Tool

- Menu Tool

- Splitter

- - Probe

- **™** Clock

- A Label

#### **Gates library**

- Constant

- NOT Gate

- > Buffer

| DDD AND/OR/NAND/NOR Gate             |

|--------------------------------------|

| 8 P A AND/OK/NAMD/NOK Gate           |

| NOR/XNOR/Odd Parity/Even Parity Gate |

| 1 1 A XON ALVON OUR TAINLY CARE      |

|                                      |

### **Memory library**

DIJKSR D/T/J-K/S-R Flip-Flop

Register Register

RAM RAM

ROM ROM

### **Plexers library**

- Multiplexer

- O Demultiplexer

- O Decoder

- **Bit Selector**

### **Arithmetic library**

- + Adder

- Subtractor

- **▼** Multiplier

- **→** <u>Divider</u>

- -× Negator

- **Comparator**

### **Legacy library**

- DJK Logisim 1.0 D/J-K Flip-Flop

- Logisim 1.0 8-Bit Register

## **Base library**

The Base library includes general-purpose tools, as well as components whose behavior in a circuit is distinguished from other components (that is, they are treated unusually by Logisim's propation engine).

- Poke Tool

- Select Tool

- Wiring Tool

- A Text Tool

- Menu Tool

- **←** Splitter

- Pin Pin

- Probe

- <u> Clock</u>

- A Label

**Library:** Base

Introduced: 2.0 Beta 1

#### Behavior

The Poke Tool is for manipulating the current values associated with components. The precise behavior of the Poke Tool varies depending on which component is clicked; this behavior is documented in the 'Poke Tool Behavior' section of each individual component. The following components all have support for the Poke Tool.

Base library Pin

Clock

Memory library D/T/J-K/S-R Flip-Flop

Register

<u>RAM</u>

**Legacy library** Logisim 1.0 D/J-K Flip-Flop

Logisim 1.0 8-Bit Register

Also, clicking a wire segment using the Poke tool displays the value currently carried by the wire, as described on the Wiring Tool's page.

#### **Attributes**

None. Clicking on a component supporting the Poke Tool, though, will display that component's attributes.

Library: <u>Base</u>

Introduced: 2.0 Beta 1

#### **Behavior**

Allows individual components to be placed into the current selection. There are a number of actions possible with this tool.

• Pressing the mouse button while it is within a currently selected component begins a drag moving all components of the selection.

Dragging a selection can lead to unexpected behavior from wires: If you drag a selection including some wires on top of some other wires, all wires are merged, and the merged wires are placed into the selection. As a result, if you drag the selection a second time, the wires previously at the location will not be left behind. This behavior is necessary to keep with the expected behavior of wires in Logisim. And it does not normally constitute a major problem: Logisim will draw the full selection in the midst of dropping, and you should not drop it until you are sure it is in the correct location.

- Otherwise, clicking the mouse within a component drops all components from the current selection and selects instead the component(s) containing the clicked location.

- Shift-clicking the mouse within a component toggles that component's presence

within the selection. If multiple components include the same location, all

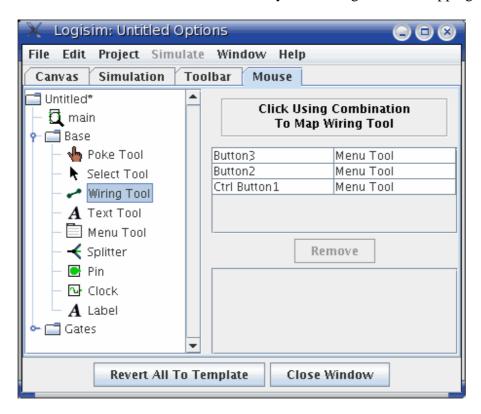

components' presence will be toggled. None of this will happen, though, if shiftclicking is mapped to another tool instead (via the project options window's

Mouse tab).

- Dragging the mouse starting at a location not contained within any components drops all components from the current selection and initiates a rectangular selection. All component(s) contained by the rectangle will be placed into the selection.

- Shift-dragging the mouse starting at a location not contained within any components initiates a rectangular selection. The presence in the selection of all component(s) contained by the rectangle will be toggled. This will not happen, though, if shift-clicking is mapped to another tool instead.

After selecting the desired items in the selection, you can of course cut/copy/paste/delete all the items via the <u>Edit menu</u>.

Logisim's behavior when pasting the clipboard into a circuit is somewhat peculiar: It will not immediately place the components into the circuit; instead, the selection will be a collection of "ghosts," which will be dropped into the circuit as soon as they are either dragged to another location or removed from the selection. (This peculiar behavior is necessary because pasting will otherwise merge the wires of the selection into the current circuit at once, and the wires there previously will be dragged with the pasted clipboard if the user wants to move the pasted components somewhere else.)

#### **Attributes**

None. Selecting a component, though, will display its attributes.

**Library:** Base Introduced: 2.0 Beta 1

#### **Behavior**

The wiring tool is the tool for creating wire segments that carry values from one endpoint to another. The bit width of these values can be anything; exactly which bit width is automatically inferred from the components to which the wires are ultimately attached. If it is not attached to any components, the wire will be drawn gray to indicate that its bit width is unknown; if the components at the locations that the wire helps to connect disagree on the bit width, then the wire will be drawn orange to indicate the conflict, and the wire will in fact refuse to carry any values at all until the user resolves the conflict.

A single drag of the mouse can create multiple wire segments. The precise process is a little confusing in its description; but it works quite intuitively in practice: If you request a particular wire segment using the Wiring Tool, that segment will be split apart wherever it hits a pin for an existing component, or wherever it hits the endpoint of an existing wire segment. Also, if an endpoint of any of the new wire segments hit somewhere in the middle of an existing wire, then that wire will be split into multiple segments itself.

For some components that draw short stubs to which wires can connect (such as an <u>OR</u> <u>gate</u> or a <u>controlled buffer</u>), Logisim will silently correct attempts to create wires that slightly overshoot the stub's end.

You can also shorten an existing wire segment using the Wiring Tool, using a drag that starts or ends at a terminus of the segment, and that overlaps the existing segment.

All wires in Logisim are either horizontal or vertical.

Wires are also non-directional; that is, they carry values from either endpoint to the other. Indeed, a wire can carry values in both directions simultaneously; the center wire in the below example is doing this.

#### **Attributes**

The wiring tool does not itself have attributes, but the wires that it creates do.

#### Direction

Indicates whether the wire is horizontal or vertical. The value of this attribute cannot be changed.

#### Length

Indicates how many pixels long the wire is. The value of this attribute cannot be changed.

#### Poke Tool Behavior

When you click an existing wire segment using the Poke Tool, Logisim displays the current value traveling through that wire. This is illustrated in the above screen shot of a wire carrying values in both directions simultaneously. The behavior is particularly useful for multi-bit wires, whose black color provide no visual feedback about what value the wire is carrying.

### AText Tool

**Library:** Base

Introduced: 2.0 Beta 1

#### Behavior

The text tool allows you to create and edit labels associated with components. Which components support labels are indicated in the 'Text Tool Behavior' section of their documentation. As of the current release, three components in the built-in libraries support labels.

Base library Pin Clock Label

Clicking on one of these components using the text tool indicates that you wish to edit the label associated with that component, even if you click the component nowhere near where the label will actually appear. Clicks at other locations indicate that you wish to create a new label component.

In the current version of Logisim, text editing features are still fairly primitive. Selections of a region of text within a label is impossible. There is no way to insert a line break into a label.

#### **Attributes**

The attributes for the tool are the same as for the <u>label component</u>. These attributes have no effect when editing the label on an existing component, but they are imparted to any labels created using the text tool.

Clicking on a component supporting the Text Tool will display that component's attributes.

Back to Library Reference

**Library:** Base

Introduced: 2.0 Beta 1

#### **Behavior**

The menu tool permits the user to pull up a pop-up menu for components that already exist. By default, right-clicking or control-clicking a component will bring up this pop-up menu; however, the Mouse tab of the project options allows a user to configure the mouse buttons to work differently.

The pop-up menu for most components has two items.

- Delete: Removes the component from the circuit.

- Show Attributes: Places the component's attributes into the window's attribute table, so that the attribute values can be viewed and changed.

For some components, however, the menu has additional items. Subcircuits (that is, instances of using one circuit as a "black box" within another) are one example of this: In addition to the above two items, the pop-up menu includes another item.

• View XXX: Changes the circuit layout being viewed and edited to be the subcircuit's layout instead. The values seen in the layout will be part of the same hierarchy as those of the supercircuit. (See the `Debugging subcircuits' section of the *User's Guide*.)

Other components may extend the pop-up menu also. In the built-in libraries of the current version of Logisim, the only such component is <u>RAM</u>.

#### **Attributes**

None.

Back to Library Reference

Library: Base

**Introduced:** 2.0 Beta 1

Appearance:

#### **Behavior**

The splitter is intended for corresponding subsets of bits to the bits within a multi-bit value. Despite its name, it can either split a multi-bit value into component parts, or it can combine component parts into a multi-bit value, or it can do both at once. A more complete description of splitters is found in the `Splitters' section of the *User's Guide*.

Logisim treats splitters specially when propagating values within a circuit: Whereas all other components have a computed delay for purposes of simulating their behavior, values propagate through splitters (as well as wires) instantaneously.

**Note:** The term *splitter* is a non-standard term, which is unique to Logisim as far as I know. I am unaware of any standard term for such a concept; the only term I have heard used is *bus ripper*, but this term is unnecessarily violent for my tastes.

#### **Pins**

To distinguish the several connecting points for a splitter, we refer to the single connecting point one side as its *combined end*, and we refer to the multiple connecting points on the other side as its *split ends*.

Combined end (input/output bit width matches Bit Width attribute)

A value holding all of the bits traveling through the splitter.

Split ends (input/output, bit width computed based on Bit *x* attributes)

The number of split ends is specified in the Fan Out attribute, and each split end has an index that is at least 0 and less than the Fan Out attribute. For each split end, all bits for which Bit *x* refers to its index travels through that split end; the order of these bits is the same as their order within the combined end.

#### **Attributes**

Facing

The location of the split ends relative to the combined end.

Fan Out

The number of split ends.

Bit Width

The bit width of the combined end.

Bit x

The index of the split end to which bit *x* of the combined end corresponds. The split ends are indexed starting from 0 at the top (for a splitter facing east or west) or from 0 at the left/west (for a splitter facing north or south). A bit can be specified to correspond to none of the split ends. There is no way for a bit to correspond to multiple split ends.

#### Poke Tool Behavior

None.

#### Text Tool Behavior

None.

Library: Base

**Introduced:** 2.0 Beta 1

Appearance: 0

#### Behavior

A pin is an output or an input to a circuit, depending on the value of its Output? attribute. In drawing a pin, Logisim represents output pins using a circle or rounded rectangle, and input pins are represented using squares or rectangles. In either case, the individual bits of the value being sent or received is displayed within the component (except within printer view, when the component only says how many bits wide the pin is).

A pin is a convenient component for interacting with a circuit, and beginning Logisim users will see this as the end of their uses. But a user building a circuit using several subcircuits (as described in the `Subcircuits' section of the *User's Guide*) will use pins also to specify the interface between a circuit and a subcircuit. In particular, a circuit layout's pin components define the pins that appear on the subcircuit component when the layout is used within another circuit. In such a circuit, the values sent and received to those locations on the subcircuit component are tied to the pins within the subcircuit layout.

#### **Pins**

A pin component has only one pin, which will be an input to the component if the pin is an output pin, and it will be an output to the component if the pin is an input pin. In either case, its bit width matches the Bit Width attribute, and its location is specified by the Facing attribute.

#### **Attributes**

Facing

The side of the component where its input/output pin should be.

Output?

Specifies whether the component is an output pin or an input pin. (Note that if the pin component is an input pin, then the pin that acts as its interface within the circuit will be an output, and vice versa.)

Bit Width

The number of bits for the value that the pin handles.

Three-state?

For an input pin, this configures whether the user can instruct the pin to emit unspecified (i.e., floating) values. The attribute deals with the user interface only; it does not have any effect on how the pin behaves when the circuit layout is used as a subcircuit. For an output pin, the attribute has no effect.

#### **Pull Behavior**

For an input pin, the attribute specifies how floating values should be treated when received as an input, perhaps from a circuit using the layout as a subcircuit. With "unchanged," the floating values are sent into the layout as floating values; with "pull up," they are converted into 1 values before being sent into the circuit layout; and with "pull down," they are converted into 0 values before being sent into the circuit layout.

Label

The text within the label associated with the component.

Label Location

The location of the label relative to the component.

Label Font

The font with which to render the label.

#### Poke Tool Behavior

Clicking an output pin has no effect, although the pin's attributes will be displayed.

Clicking an input pin will toggle the bit that is clicked. If it is a three-state pin, then the corresponding bit will rotate between the three states.

If, however, the user is viewing the state of a subcircuit as described in the `Debugging Subcircuits' of the *User's Guide*, then the pin's value is pinned to whatever value the subcircuit is receiving from the containing circuit. The user cannot change the value without breaking this link between the subcircuit's state and the containing circuit's state, and Logisim will prompt the user to verify that breaking this link is actually desired.

#### Text Tool Behavior

Allows the label associated with the component to be edited.

Back to *Library Reference*

Library: Base

Introduced: 2.0.3

Appearance: 0

1010

#### **Behavior**

A probe is an element that simply display the value at a given point in a circuit. It does not itself interact with other components.

In most respects, the probe component duplicates the functionality found in a <u>Pin</u> <u>component</u> configured as an output pin. The only difference is that if the circuit is used as a subcircuit component, then an output pin will be a part of that interface, whereas a probe is not. Graphically, they are similar but have slightly different borders: A pin has a thick, black border, whereas a probe has a thin, gray border.

#### **Pins**

A probe component has only one pin, which will acts as an input to the probe. The width that this pin accepts is adaptive: The probe will adapt to inputs of any width.

#### **Attributes**

Facing

The side of the component where its input pin should be.

Label

The text within the label associated with the component.

**Label Location**

The location of the label relative to the component.

Label Font

The font with which to render the label.

#### Poke Tool Behavior

None.

#### Text Tool Behavior

Allows the label associated with the component to be edited.

## **□** Clock

Library: Base

**Introduced:** 2.0 Beta 13

Appearance:

#### **Behavior**

The clock toggles its output value on a regular schedule as long as ticks are enabled via the <u>Simulate menu</u>. (Ticks are disabled by default.) A "tick" is Logisim's unit of time; the speed at which ticks occur can be selected from the Simulate menu's Tick Frequency submenu.

The clock's cycle can be configured using its High Duration and Low Duration attributes.

Note that Logisim's simulation of clocks is quite unrealistic: In real circuits, multiple clocks will drift from one another and will never move in lock step. But in Logisim, all clocks experience ticks at the same rate.

#### **Pins**

A clock has only one pin, an output with a bit width of 1, whose value will represent the current value of the clock. The location of this pin is specified in the Facing attribute. The clock's value will toggle on its schedule whenever ticks are enabled, and it will toggle whenever it is clicked using the <u>Poke Tool</u>.

#### **Attributes**

Facing

The side of the component where its output pin should be.

**High Duration**

The length of time within each cycle that the clock's output should be 1.

Low Duration

The length of time within each cycle that the clock's output should be 0.

Label

The text within the label associated with the clock component.

Label Location

The location of the label relative to the component.

Label Font

The font with which to render the label.

#### Poke Tool Behavior

Clicking a clock component will toggle its current output value immediately.

#### Text Tool Behavior

Allows the label associated with the component to be edited.

## $\mathbf{\underline{B}}$ $\mathbf{A}$ Label

**Library:** Base

**Introduced:** 2.0 Beta 1 **Appearance:** Text Label

#### Behavior

This is a simple text label that can be placed anywhere in the circuit. It does not interact with values traveling through the circuit in any way, except inasmuch as it will be visible when the circuit is drawn.

In contrast to all other components in the current built-in libraries, label components can be placed anywhere on the canvas; they do not snap to the grid.

#### **Pins**

None.

#### **Attributes**

Text

The text appearing in the label. This value can be edited in the attribute table or, using the text tool, on the canvas.

Font

The font to use when drawing the label.

#### Horizontal Alignment

The horizontal positioning technique for the text relative to the label's official location (where the mouse was clicked in creating the label). "Left" means that the text should be drawn so that its left edge is at the location; "right" means that the text should be drawn so that its right edge is at the location; and "center" means that the text should be drawn so that its center (horizontally) is at the location.

#### Vertical Alignment

The vertical positioning technique for the text relative to the label's official location (where the mouse was clicked in creating the label). "Base" means that the baseline should intersect the location; "Top" means that the text's top should intersect the location; "Bottom" means that the text's bottom should intersect the location; and "Center" means that the text should be centered (vertically) at the location.

The text's top and bottom is computed based on the font's standard ascent and descent values; thus, even if the actual text contains no tall letters (such as *b*) or descending letters (such as *g*), it is assumed to contain such letters for the purposes of vertical positioning.

#### Poke Tool Behavior

None.

#### Text Tool Behavior

Allows the text appearing within the label to be edited.

Back to Library Reference

ack to Library Reference

## **Gates library**

The Gates library includes a variety of simple components, all of which have a single output whose value is dictated entirely by the current inputs.

Library: <u>Gates</u>

**Introduced:** 2.0 Beta 1

Appearance: 1.

#### Behavior

Emits the value specified in its Value attribute.

#### **Pins**

There is only one pin, an output whose bit width matches the Bit Width attribute. The location of this pin is specified in the Facing attribute. The component constantly outputs on this pin whatever value specified in the Value attribute.

#### **Attributes**

Facing

The direction in which the pin is located relative to where the value is drawn.

Bit Width

The bit width of the component's inputs and outputs.

Value

The value, written in hexademical, that is emitted by the component. The number of bits used to specify the value cannot exceed the component's bit width.

#### Poke Tool Behavior

None.

#### **Text Tool Behavior**

None.

Back to Library Reference

Library: <u>Base</u>

**Introduced:** 2.0 Beta 1

Appearance: Shaped

Rectangular 1

#### **Behavior**

The NOT Gate emits the complement of whatever input it receives. The truth table for a NOT gate is the following.

x out0 11 0

If the input is unspecified (i.e., floating), or if it is the error value, then the output will have the same value.

A multi-bit NOT gate will perform the above transformation bitwise on its input.

#### **Pins**

West edge (input, bit width according to Bit Width attribute)

The component's input.

East edge (output, bit width according to Bit Width attribute)

The output, whose value is the complement of the input value.

#### **Attributes**

Facing

The direction of the component (its output relative to its input).

Bit Width

The bit width of the component's inputs and outputs.

Gate Size

Determines whether to draw a larger or a smaller version of the component.

#### Poke Tool Behavior

None.

#### Text Tool Behavior

None.

## **Buffer**

**Library:** <u>Base</u>

**Introduced:** 2.0 Beta 1

Appearance: >

#### Behavior

The buffer simply passes through to its right output whatever input it receives on the left side. The truth table for a one-bit buffer is the following.

x out

0 0

1 1

Buffers are beyond question the most useless of the gate components provided in Logisim; its presence in the Gates library is just as much a matter of completeness (a component for each possible one-input truth table) as it is a matter of providing useful functionality. Still, it can be occassionally useful to ensure that values propagate in only one direction along a wire.

#### **Pins**

West edge (input, bit width according to Bit Width attribute)

The input into the component.

East edge (output, bit width according to Bit Width attribute)

The output, which always matches the input into the left side.

#### **Attributes**

Facing

The direction of the component (its output relative to its input).

Bit Width

The bit width of the component's inputs and outputs.

#### Poke Tool Behavior

None.

#### Text Tool Behavior

None.

**Library:** Base

Introduced: 2.0 Beta 1

Appearance:

Shaped

Rectangular

AND OR NAND NOR

Shaped

Sha

#### **Behavior**

The AND, OR, NAND, and NOT gates each compute the respective function of the inputs, and emit the result on the output. The two-input truth table for the gates is the following.

| xy  | AND | OR | NAND | NOR |

|-----|-----|----|------|-----|

| 00  | 0   | 0  | 1    | 1   |

| 0 1 | 0   | 1  | 1    | 0   |

| 10  | 0   | 1  | 1    | 0   |

| 1 1 | 1   | 1  | 0    | 0   |

Any inputs that are unspecified (i.e., floating) are ignored; the AND and OR gates compute the AND/OR of all specified inputs, and the NAND/NOR gates compute the complement of the AND/OR of all specified inputs. If all inputs are floating, then the output is floating, too. If any of the inputs are the error value (e.g., if conflicting values are coming into the same wire), then the output will be the error value, too.

The multi-bit versions of each gate will perform its one-bit transformation bitwise on its inputs.

#### Pins

West edge (inputs, bit width according to Bit Width attribute)

The inputs into the component. There will be as many of these as specified in the Number of Inputs attribute.

Note that if you are using shaped gates, the west side of OR and NOR gates will be curved. Nonetheless, the input pins are in a line. Logisim will draw short stubs illustrating this; and if you overshoot a stub, it will silently assume that you did not mean to overshoot it. In "printer view", these stubs will not be drawn unless they are connected to wires.

East edge (output, bit width according to Bit Width attribute)