## **Design of CMOS Synchronous Sequential Circuit:**

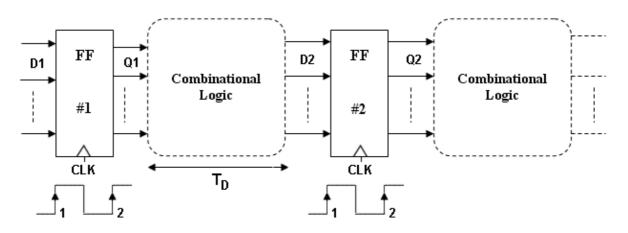

• A synchronous sequential circuit basically looks like this:

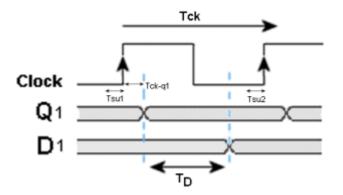

• Based on the FF & combinational logic timing parameters, the following timing constraints are obtained for correct operation of the circuit:

$$\rightarrow T_{ck} \geq T_{ck \rightarrow q1} + T_D + T_{su}$$

$T_D$  = worst case delay through combinational logic

- This assumes that the clock arrives at all **FFs**, at exactly the same time!

- <u>Clock Skew</u> ( $T_{skew}$ ) is the delay between clocks at different chip locations.

- To take Skew into account:

$$\rightarrow \mathbf{T}_{ck} \geq \mathbf{T}_{ck \rightarrow q1} + \mathbf{T}_{D} + \mathbf{T}_{su} + \mathbf{T}_{skew}$$

- Clock Signals will have random variations in their Periods and Frequencies, called Jitter.

- We have to take into account the <u>Peak to Peak Jitter</u>  $(T_{P-P Jitter})$ :

$$\rightarrow \mathbf{T}_{ck} \geq \mathbf{T}_{ck \neq q1} + \mathbf{T}_{D} + \mathbf{T}_{su} + \mathbf{T}_{skew} + \mathbf{T}_{P-P \text{ Jitter}}$$

• Another Timing Constraint arises in situations where  $T_D$  is "Zero" or very small when the output of a FF is fed directly to the input of another (e.g. in Shift Registers). In such situation, we need to make sure that the data does not pass

through two FFs (during the transparency window of the FF where both master and slave are enabled). Hence to avoid Hold Time violation:

$T_{skew} + T_{P-P \text{ Jitter}} + T_{hold2} \le T_{ck \rightarrow q1} + T_D$

Where  $T_{hold2}$  is the hold time of the  $2^{nd}$  FF

## Synchronous Circuit Design Mythology:

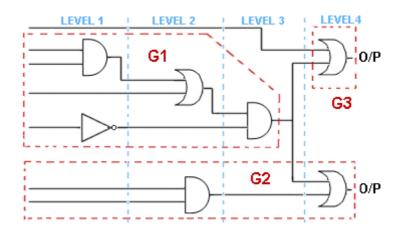

- Through Logic Transformations, transfer the logic between the FFs into CMOS Gates with minimum number of Logic Levels <u>And/OR</u> minimum number of Transistors:

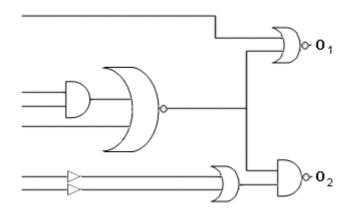

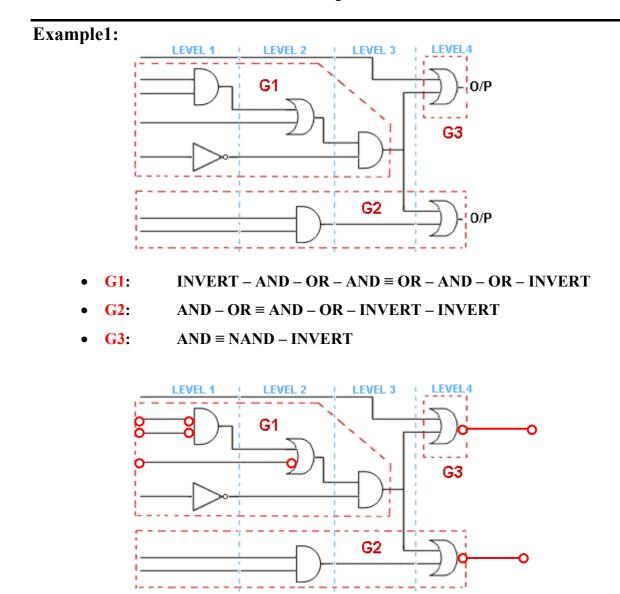

- $\mathfrak{B}1^{st}$ . Combine as many gates into single complete gates:

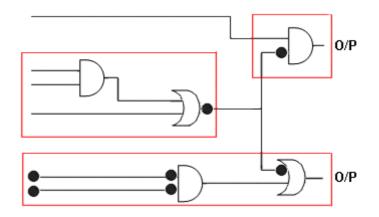

any cluster or group of gates that have single O/P can be combined into a single gate. Example:

Starting from Logic Level One (the closest to the I/Ps), convert into CMOS using the following logic transformations:

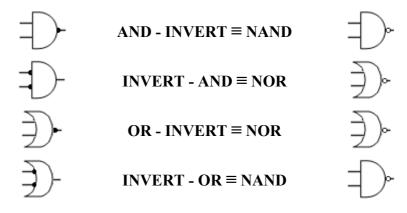

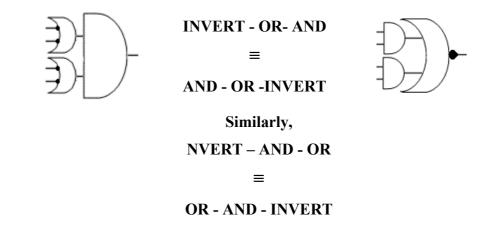

S<sup>rd</sup>. Gates are converted by inserting <u>Bubbles</u>, in pairs, either at the I/Ps or O/Ps & transfer the gates into CMOS.

• The Transformed Circuit:

$\rightarrow$  4 Logic Levels  $\rightarrow$  28 Transistors ; Original Circuit had 4 Logic Levels

Solution The number of Logic Levels in the Transformed Circuit should not exceed the Original Circuit by, at most, more than <u>one extra level of inverters</u>.

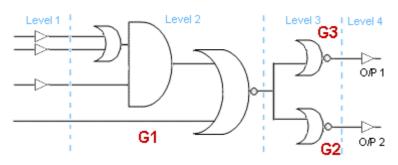

**Example2:** The following Circuit is implemented in CMOS (original circuit without the black bubbles):

• This is the Transformed Circuit: