| Register transfer / logic | Idea<br>chitectural design<br>Logical design<br>Physical design<br>Fabrication | Generic CAD tools<br>Behavioral modeling and<br>Simulation tool<br>Functional and logic minimization<br>logic fitting and simulation tools<br>Tools for partitioning,<br>placement, routing, etc. |

|---------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## Architectural Design

- Generally carried out by expert human engineers.

- Decisions made effect cost/performance of the design. Some examples are

- » What should be the instruction set (IS) of the Processor (P)?

- What memory addressing modes should be supported?

- Should the IS be compatible with another in the market?

- » Should instruction pipelining be employed?

- If yes, then what should be the depth?

- » Should the P be provided by an on-chip cache?

- How big should the cache be?

- What should be the organization of the cache?

- Should instruction cache be separated from data cache?

1 - 5

Architectural Design

How should the arithmetic unit be designed?

Bit Serial or Bit Parallel?

Bit Serial will save on hardware but lose on performance!

How will the Processor interface to the external world?

Are there any International Standards to be met?

Notes: This level of design cannot be done by a computer program, there are tools that can aid the system Architect.

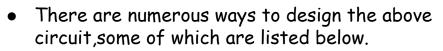

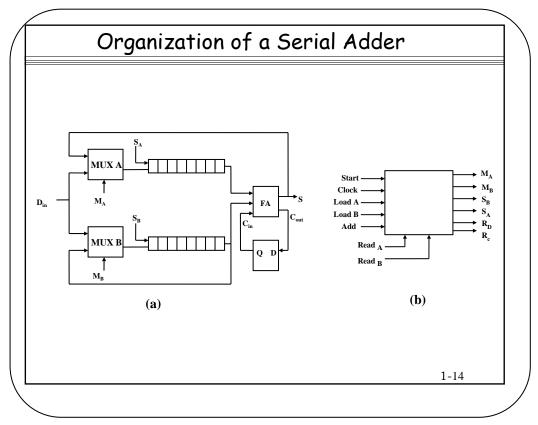

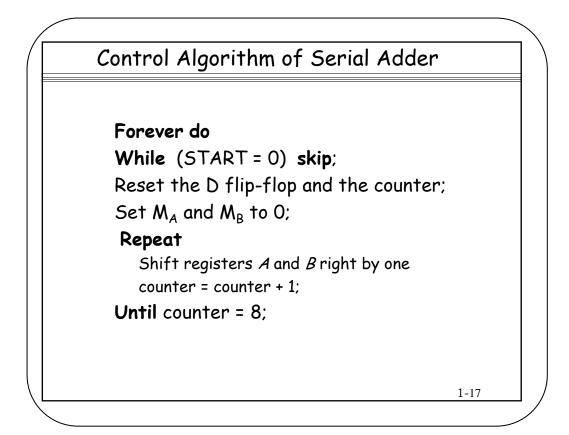

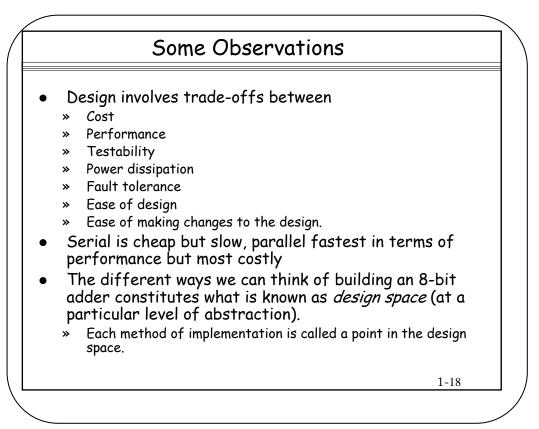

## An Example

• The Problem: It is required to design an 8-bit adder. The two operands are stored in two 8-bit shift registers A and B. At the end of the addition operation, the sum must be stored in the A register. The contents of the B register must not be destroyed. The design must be as economical as possible in terms of hardware.

- » Use an 8-bit carry look-ahead adder.

- » Use an 8-bit ripple-carry adder

- » Use two 4-bit carry look-ahead adders and ripple the carry between stages.

- » Use a 1-bit adder and perform the addition serially in 8 clock cycles.

1-12

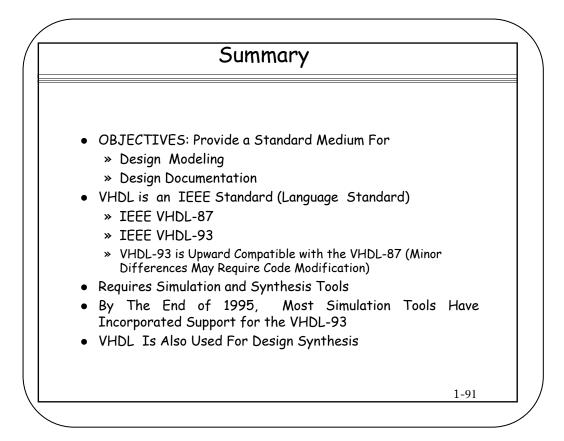

|   | Design Documentation                                                                                                            |

|---|---------------------------------------------------------------------------------------------------------------------------------|

| • | Language standardization<br>» to improve quality and efficiency of communication,                                               |

|   | broaden audience                                                                                                                |

| • | Interface description for users                                                                                                 |

|   | <ul> <li>often as components of next level higher system:<br/>physical, structural, and "pin" functions</li> </ul>              |

| • | Express usage constraints                                                                                                       |

|   | » e.g. disallowed input timings, combinations, output loads                                                                     |

| • | Express functional behavior of the design:<br>» internal states, data structures (e.g. format used in a<br>floating point unit) |

|   | » algorithms implemented                                                                                                        |

| • | Show communication protocols between design entities                                                                            |

|   |                                                                                                                                 |

|   | 1-36                                                                                                                            |

• Note: The word "synthesis" was not mentioned as one of the reasons for creating VHDL (as it was primarily intended for documentation, and modeling/simulation)

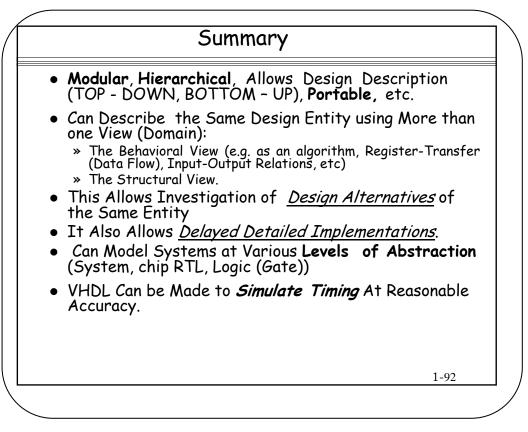

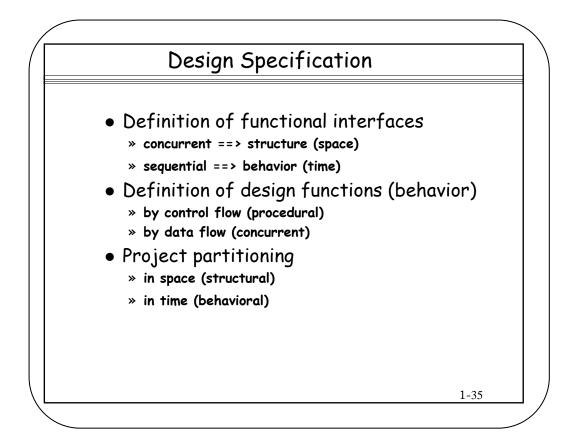

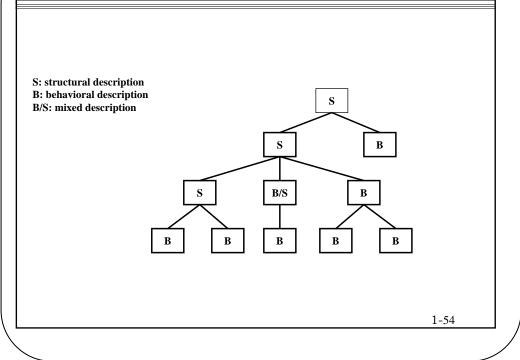

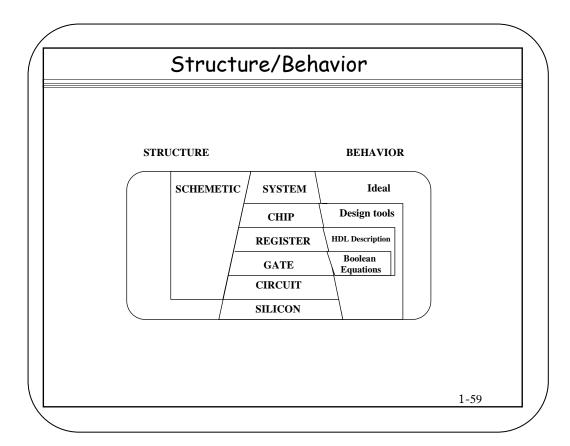

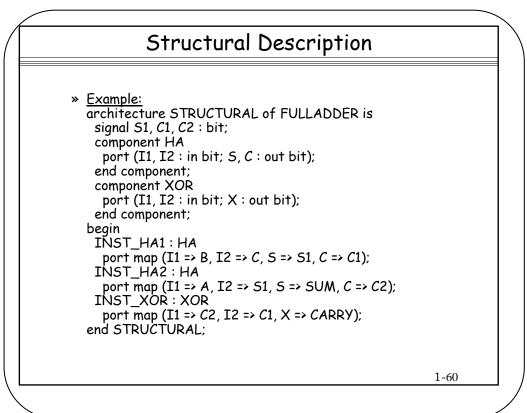

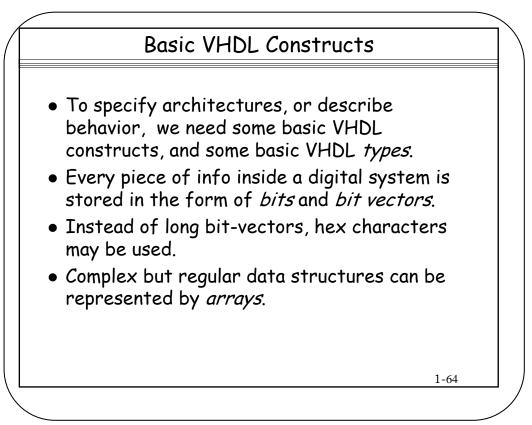

- Each system can be either in terms of its functionality (behavior) or structure, which requires different kinds of information about the system.

- Usually the synthesis tool works with both of them.

» First the expected functionality has to be specified and formalized;

- » And then it has to be transformed into structural equivalent

- » The structural equivalent is more suitable for synthesis tool

- Parts of this translation can be done automatically

- However a fully functional (behavioral) synthesis tools is not yet available.

- This is because the behavioral spec is only a description of outputs' response to inputs' changes.

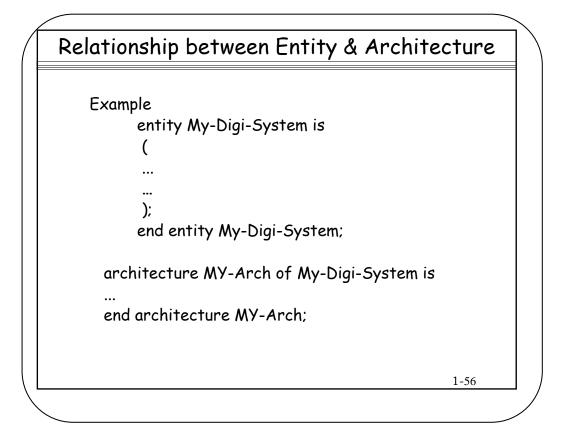

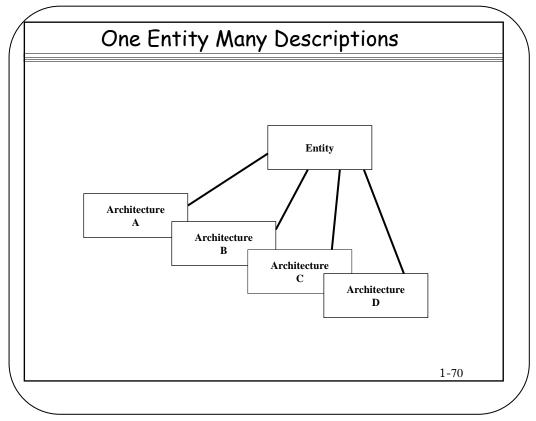

• The reverse is not true, since architectures may <u>NOT</u> have different interfaces.

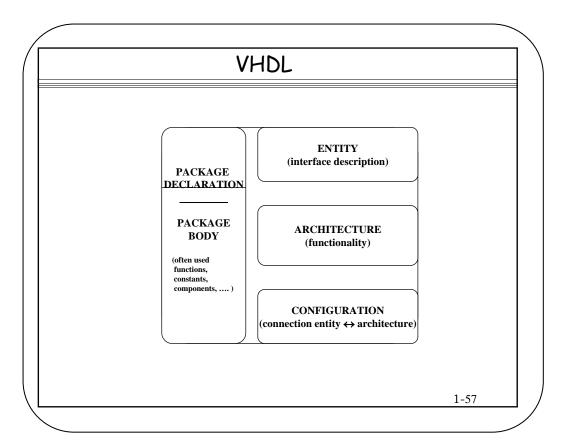

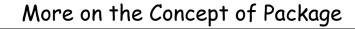

- A packages is used as a collection of often used » datatypes,

- aatatypes,

components,

- Functions, and so on.

- Once these object are declared and defined in a package, they can be used by different VHDL design units.

- In particular, the definition of global information and important shared parameters in complex designs or within a project team is recommended to be done in packages.

- It is possible to split a package into a declaration part and the so-called body.

- » Advantage is that after changing definitions in the package body only this part has to be recompiled and the rest of the design can be left untouched. Therefore, a lot of time consumed by compiling can be saved.

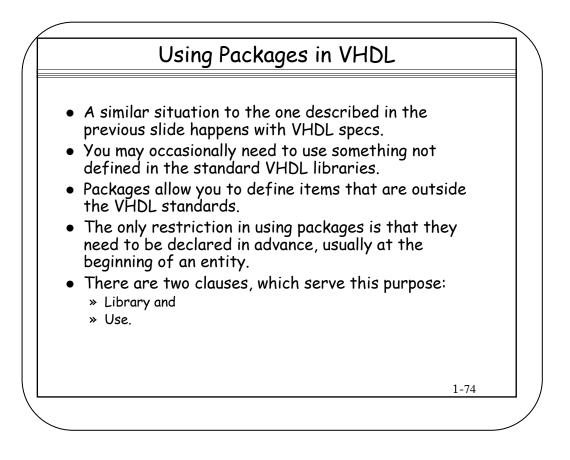

| Using Packages in VHDL                   |      |

|------------------------------------------|------|

| entity SomeSyst is                       |      |

| <br>end entity SomeSyst;                 |      |

| architecture FirstARC of SomeSyst is<br> |      |

| Logarithm<br>                            |      |

| end architecture FirstArch;              |      |

|                                          | 1-75 |

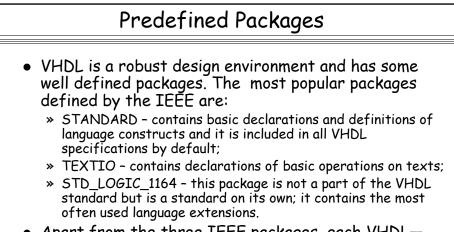

## Apart from the three IEEE packages, each VHDL tool vendor adds (and encourages to use) his/her own package.

• In such cases the library usually bears the vendor's name.

-- "don't care"

| Ones Count Interface Specification                                        |      |

|---------------------------------------------------------------------------|------|

| entity ONES_CNT is                                                        |      |

| port ( A : in BIT_VECTOR(2 downto 0);<br>C : out BIT_VECTOR(1 downto 0)); |      |

| Function Documentation of ONES_CNT<br>(Truth Table Form)                  |      |

| This is a COMMENT                                                         |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                      |      |

| end ONES_CNT;                                                             | 1-82 |