# COE 571 Digital System Testing An Introduction

Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

### Outline

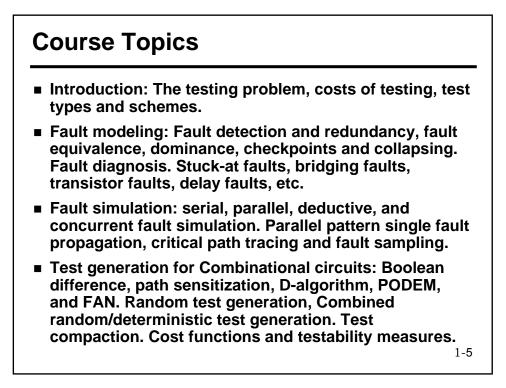

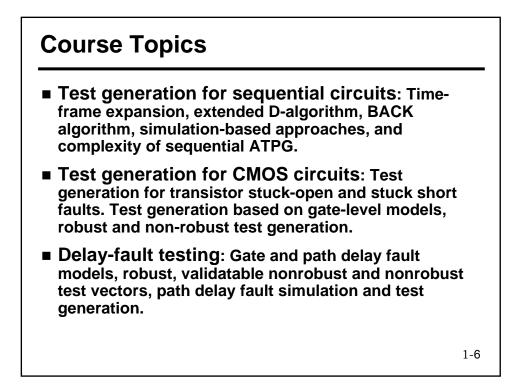

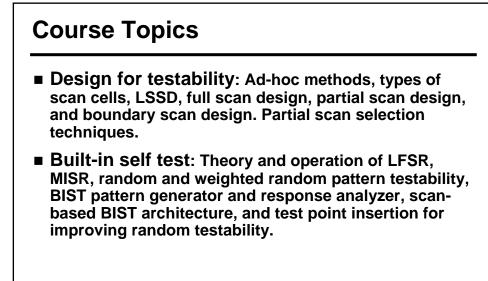

- Welcome to COE 571

- VLSI Realization Process

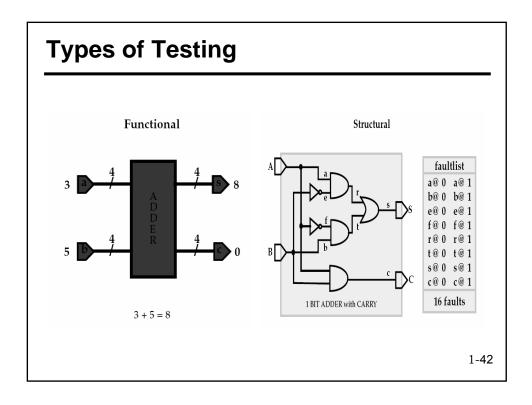

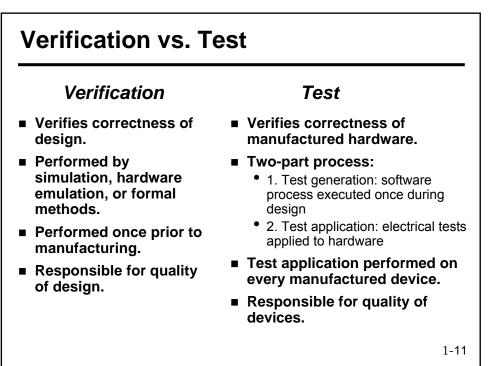

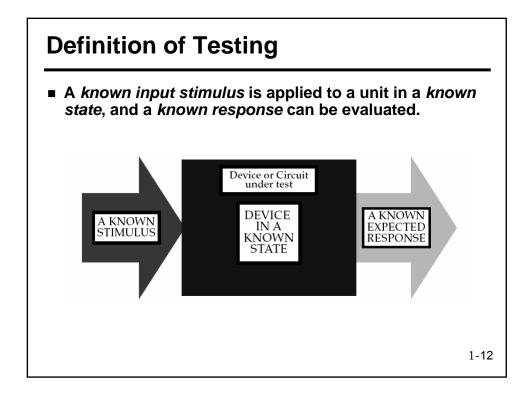

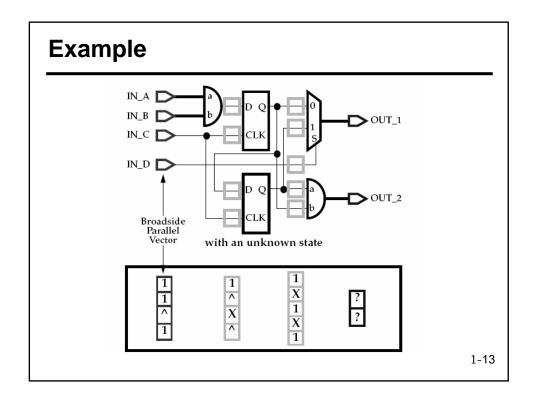

- Definition of Testing

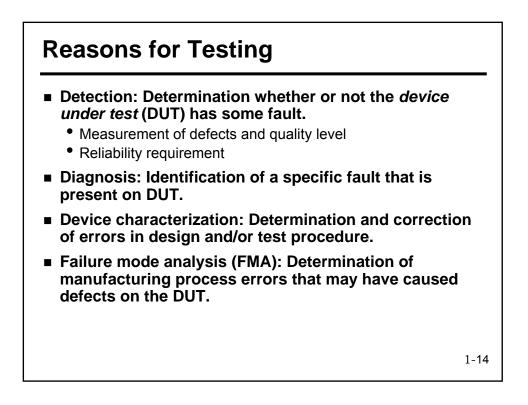

- Reasons for Testing

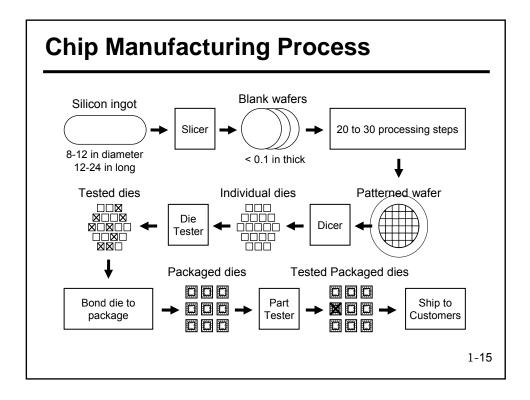

- Chip Manufacturing Process

- Manufacturing Cost

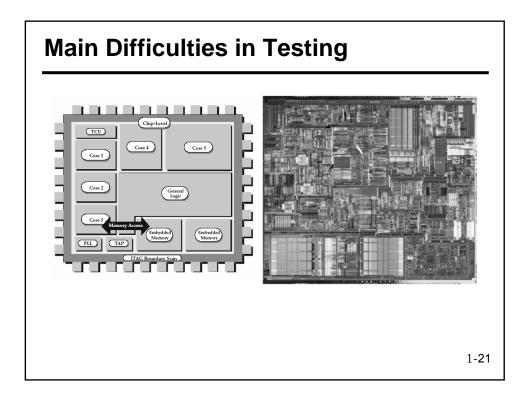

- Main Difficulties in Testing

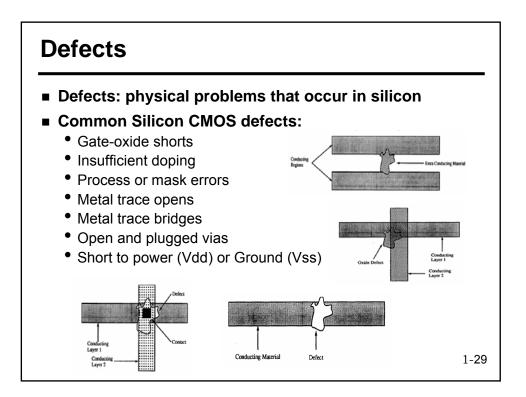

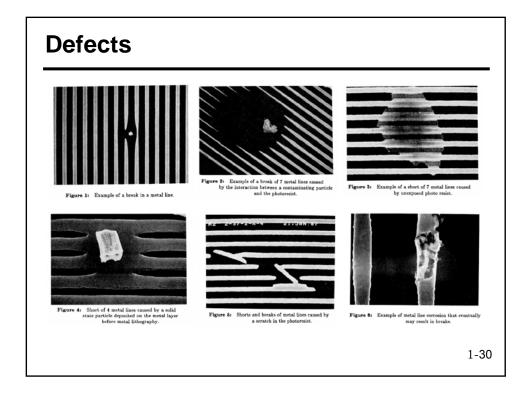

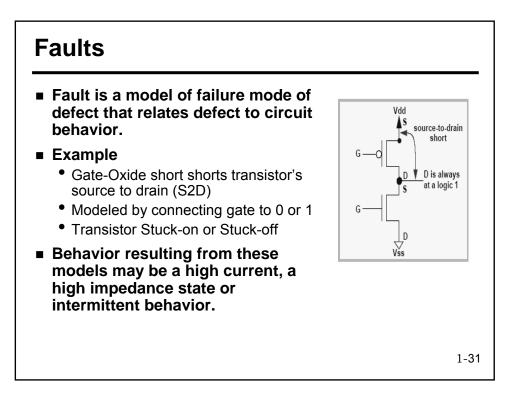

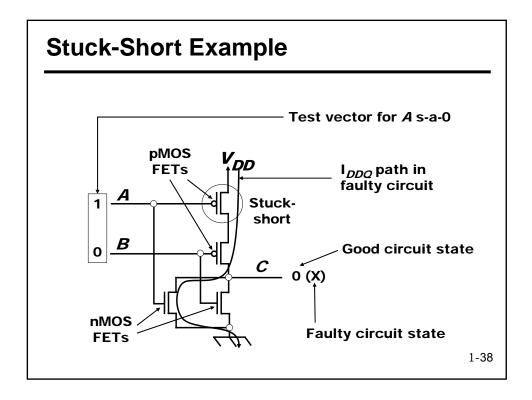

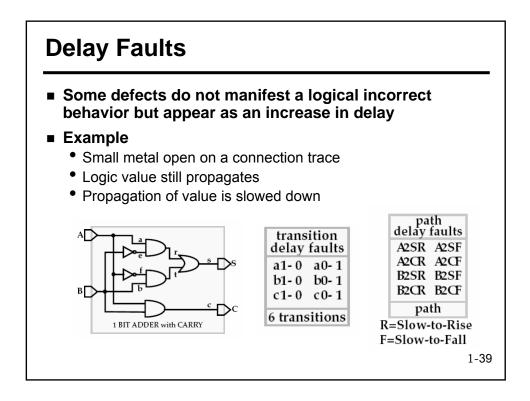

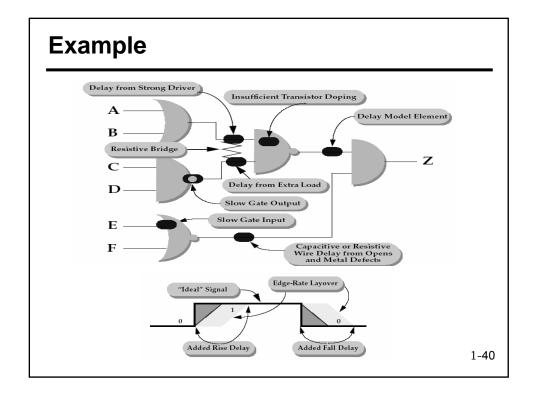

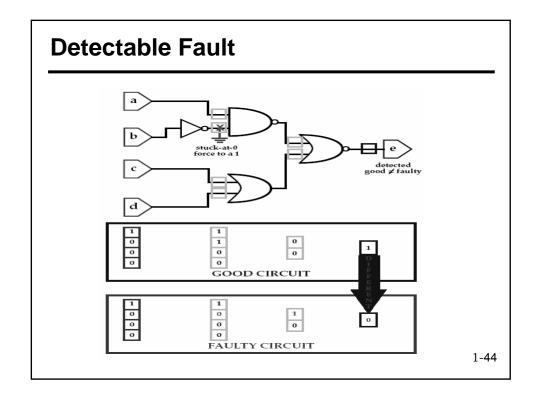

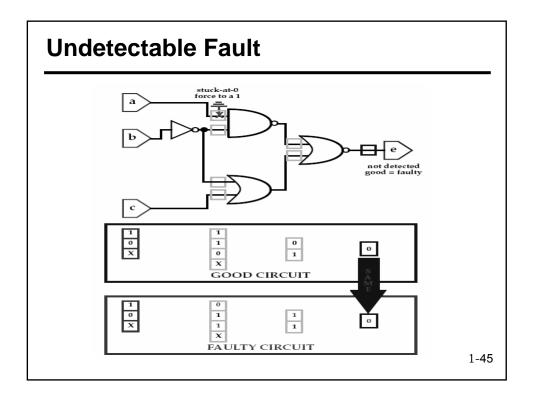

- Defects & Faults

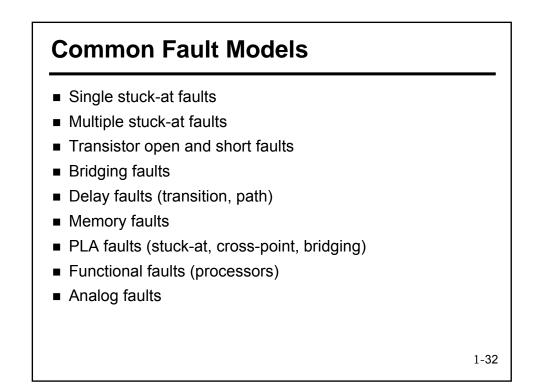

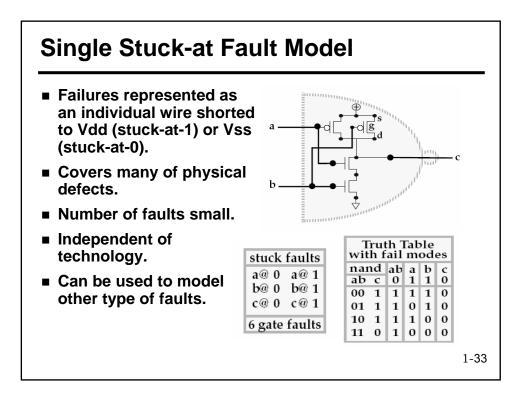

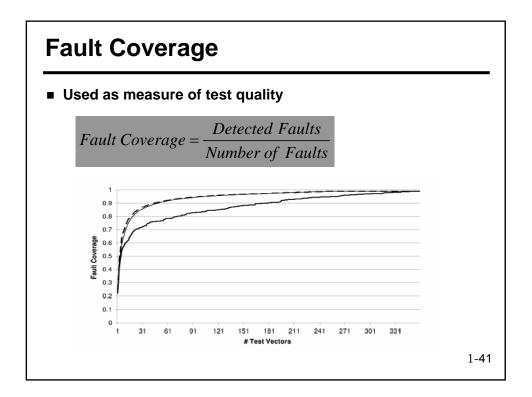

- Fault Models

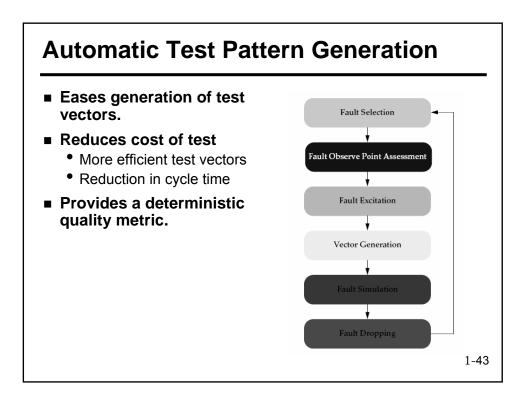

- Automatic Test Pattern Generation

| Assignments                        | 15%                                                                                                           |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Exam I                             | 15% (S., March 29, 7:00 PM)                                                                                   |

| Exam II                            | 20% (S., May 17, 7:00 PM)                                                                                     |

| Paper Presentations                | 10%                                                                                                           |

| Project                            | 20%                                                                                                           |

| no later than one week attendance. | uthorized absences must be presente<br>following resumption of class<br>be accepted (upto 3 days) but you wil |

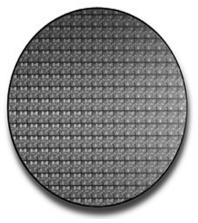

### Wafer of Pentium 4 Processors

- 8 inches (20 cm) in diameter

- Die area is 250 mm<sup>2</sup>

- About 16 mm per side

- 55 million transistors per die

- 0.18 µm technology

- Size of smallest transistor

- Improved technology uses

0.13 µm and 0.09 µm

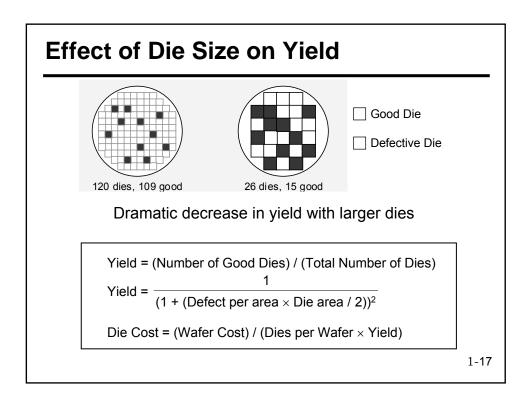

- Dies per wafer = 169

- When yield = 100%

- Number is reduced after testing

- Rounded dies at boundary are useless

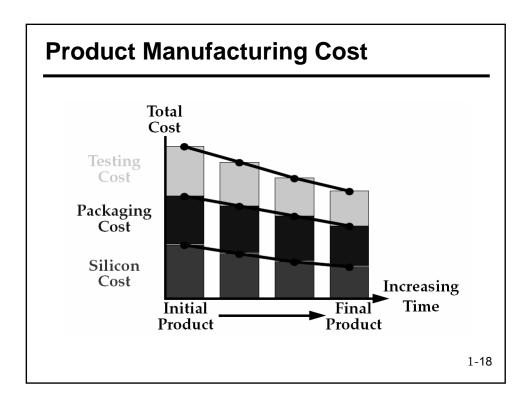

## **Product Manufacturing Cost**

#### Reduction of silicon cost

- increasing volume and yield

- die size reduction (process shrinks or more efficient layout)

### Reduction of packaging cost

- increasing volume

- shifting to lower cost packages if possible (e.g., from ceramic to plastic)

- reduction in package pin count

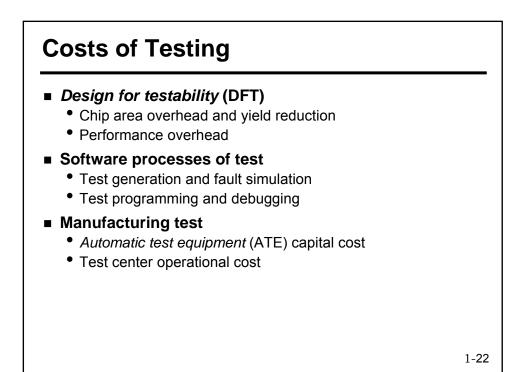

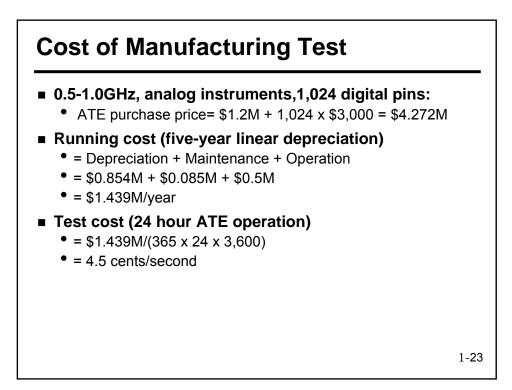

### Reduction in cost of test

- reducing vector data size

- reducing the cost of the tester

- reducing test time